Rainbow Electronics W90P710CDG User Manual

Page 513

W90P710CD/W90P710CDG

- 514 -

Continued

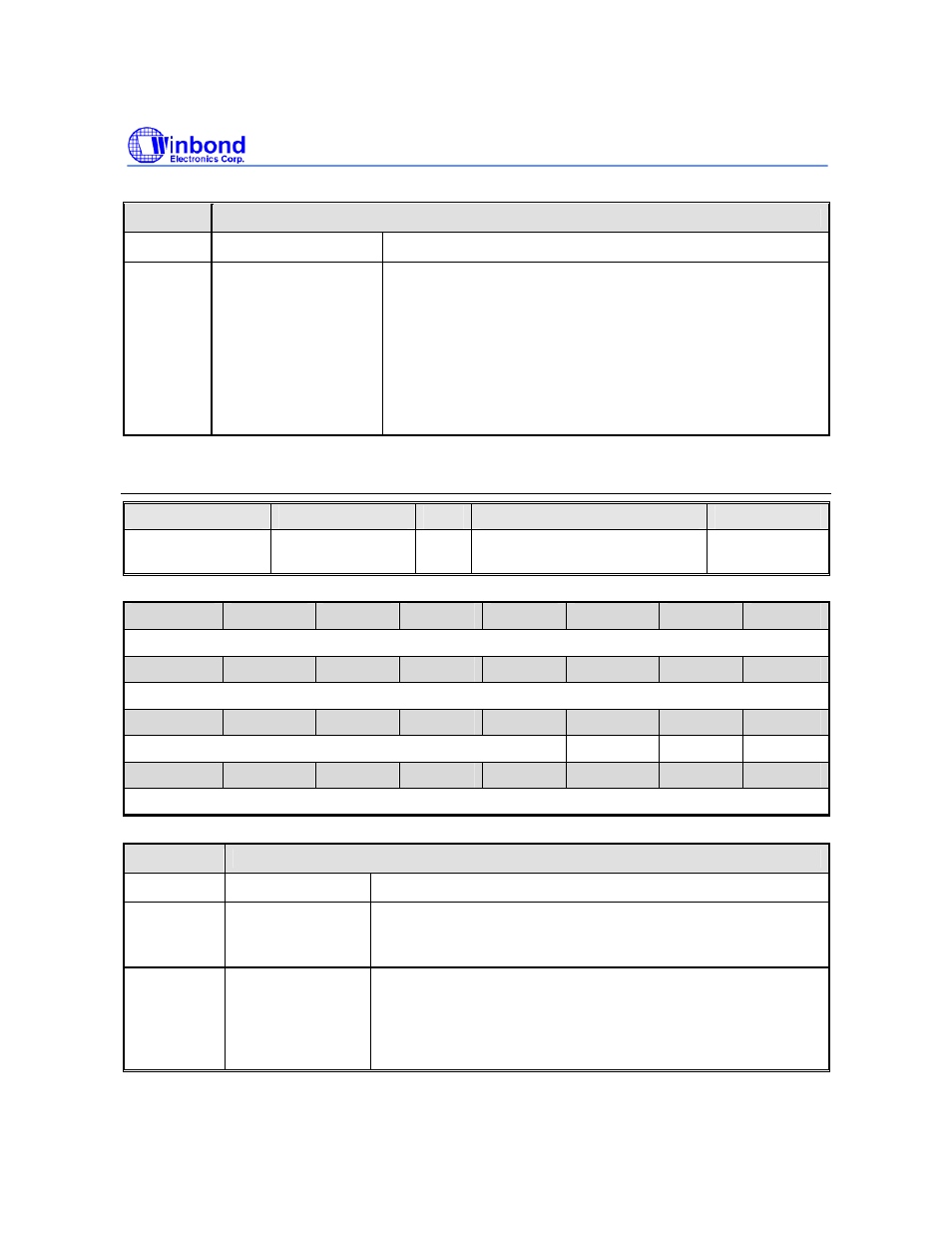

BITS

DESCRIPTIONS

[3:1]

Reserved

[0]

RX_IRQ

This Receive Interrupt bit indicates software that Host

controller receives one byte data from device. This data is

stored at PS2_SCANCODE register. Software needs to write

one to this bit to clear this interrupt after reading receiving

data in RX_SCAN_CODE register. Note that the reception of

the Extend (0xE0) and Release (0xF0) scan code will not

cause an interrupt by host. The case of the shift key codes

will be determined by the TRAP_SHIFT bit of PS2_CMD

register.

PS2 Host Controller RX Scan Code Register (PS2_SCANCODE)

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

PS2SCANCODE

0xFFFF_9008

R/W key pad c RX Scan Code

Register

0x0000_0000

31

30

29

28

27

26

25

24

RESERVED

23

22

21

20

19

18

17

16

RESERVED

15

14

13

12

11

10

9

8

RESERVED

RX_shift_key

RX_release RX_extend

7

6

5

4

3

2

1

0

RX_SCAN_CODE

BITS

DESCRIPTIONS

[31:11] RESERVED

-

[10] RX_shift_key

This Receive Shift Key bit indicates that left or right shift key on

the keyboard is hold. This bit is read only and will clear by host

when the release shift key codes are received.

[9] RX_release

Receive Released Byte

When one key has been released, the keyboard will send F0

(hex) to inform Host controller. This bit indicates software that

Host controller receives release byte (F0). This bit is read only

and will update when host has received next data byte.