Rainbow Electronics W90P710CDG User Manual

Page 129

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 129 -

Revision B2

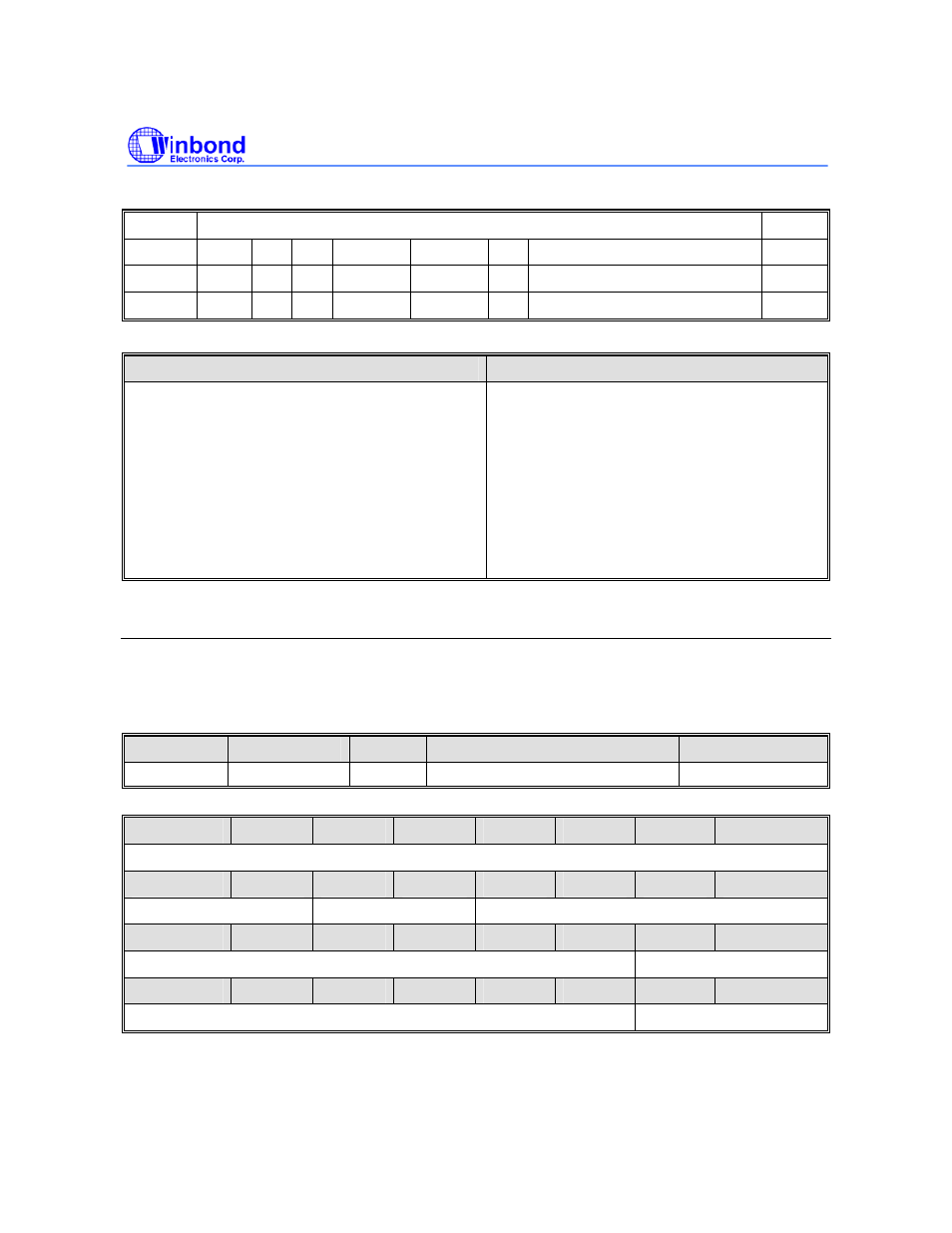

Management frame fields

PRE ST OP PHYAD REGAD

TA

DATA

IDLE

READ 1…1 01 10 AAAAA

RRRRR

Z0

DDDDDDDDDDDDDDDD

Z

WRITE 1…1 01 01 AAAAA

RRRRR

10

DDDDDDDDDDDDDDDD

Z

MII Management Function Configure Sequence

READ

WRITE

1.

Set appropriate MDCCR.

2.

Set PHYAD and PHYRAD.

3.

Set Write to 1’b0

4. Set bit BUSY to 1’b1 to send a MII

management frame out.

5.

Wait BUSY to become 1’b0.

6.

Read data from MIID register.

7.

Finish the read command.

1.

Write data to MIID register

2.

Set appropriate MDCCR.

3.

Set PHYAD and PHYRAD.

4.

Set Write to 1’b1

5. Set bit BUSY to 1’b1 to send a MII

management frame out.

6.

Wait BUSY to become 1’b0.

7.

Finish the write command.

FIFO Threshold Control Register (FFTCR)

The FFTCR defines the high and low threshold of internal FIFOs, including TxFIFO and RxFIFO. The

threshold of internal FIFOs is related to EMC request generation and when the frame transmission

starts. The FFTCR also defines the burst length of AHB bus cycle for system memory access.

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

FFTCR 0xFFF0_309C R/W

FIFO Threshold Control Register

0x0000_0101

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved BLength

Reserved

15

14

13

12

11

10

9

8

Reserved TxTHD

7

6

5

4

3

2

1

0

Reserved RxTHD