Rainbow Electronics W90P710CDG User Manual

Page 444

W90P710CD/W90P710CDG

- 444 -

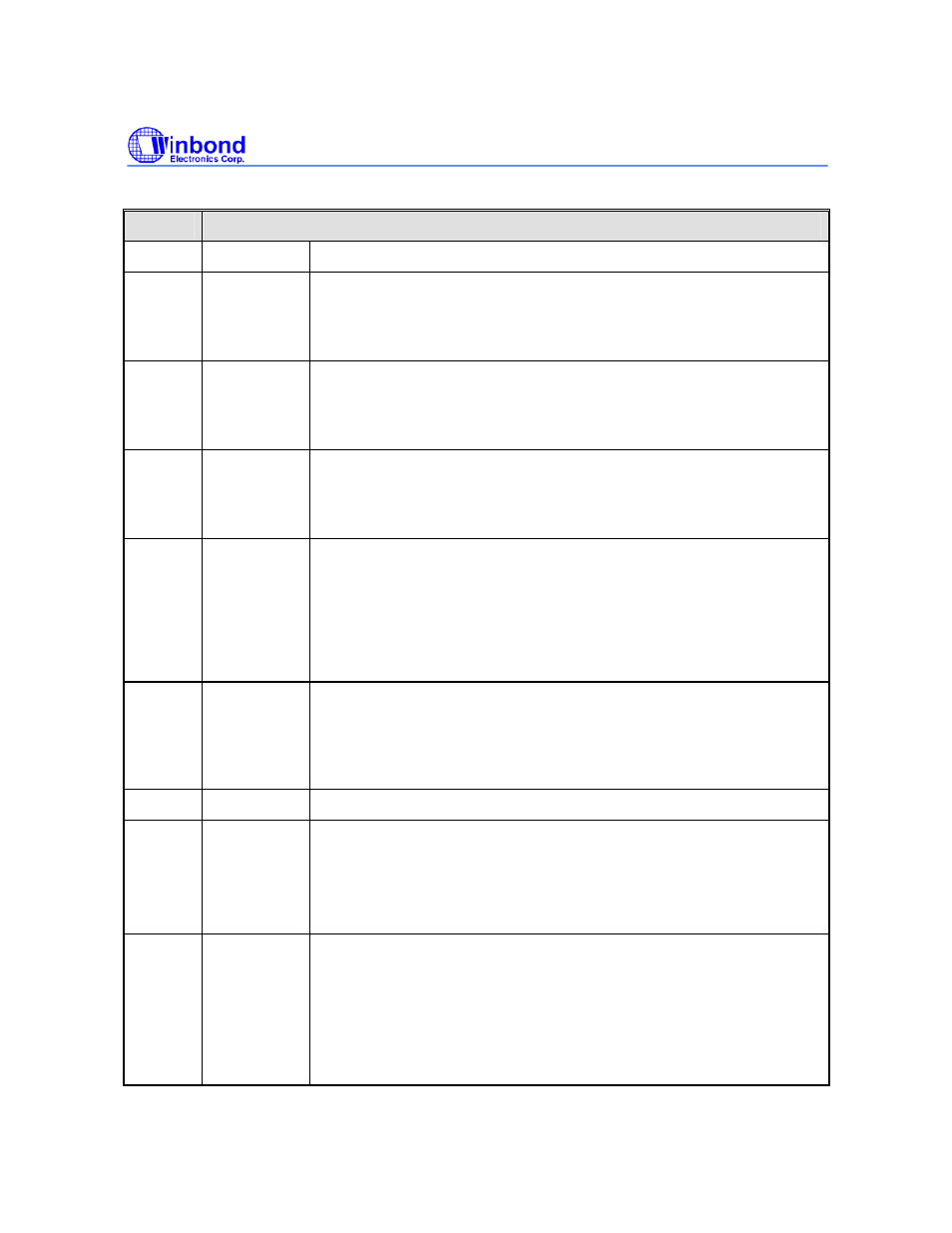

BITS

DESCRIPTIONS

[31:11]

RESERVED

-

[10]

ETOR2

TOR2 interrupt enable bit

When 24 bit time-out counter decrease to zero, it will set TO2 flag to

high. If we set ETOR2 to high, then the 24 bit time-out counters will

interrupt CPU to indicate that the time-out count is reached.

[9]

ETOR1

TOR1 interrupt enable bit

When 16 bit time-out counter decrease to zero, it will set TO1 flag to

high. If we set ETOR1 to high, then the 16 bit time-out counters will

interrupt CPU to indicate that the time-out count is reached.

[8]

ETOR0

TOR0 interrupt enable bit

When 8 bit time-out counter decrease to zero, it will set TO0 flag to high.

If we set ETOR0 to high, then the 8 bit time-out counters will interrupt

CPU to indicate that the time-out count is reached.

[7]

PWRDN

Smart card POWER DOWN bit

PWRDN is used when the Smartcard controller needs to be powered

down. Powering down must be done whenever the controller needs to

switch between class A and B. When this bit is a ‘1’, it will deactivate all

contacts to the Smartcard except for SCRST_L which will be discussed

later.

When the Smartcard is removed, the H/W will also set the POWER

DOWN bit.

[6]

Interface

Smart card different interface bit

Interface is used for controlling the different power control device

signals. When ‘1’, the controller will direct a power control pin is active

high. When ‘0’, a power control pin is active low to meet different power

control interface.

[5:4] RESERVED Reserved for future

[3]

ESCPTI

Smart card present toggle interrupt enable bit

A rising/falling edge of SCPSNT signal triggers an interrupt if this bit is

set to "1".

0 = SCPSNT toggle interrupt is disabled.

1 = SCPSNT toggle interrupt is enabled.

[2]

ESCSRI

Enable SCSR interrupt bit

An ESCSRI means interrupt enable bit for SCSR-related events such as

silent byte detected error, no stop bit error, parity bit error or overrun

error. Any SCSR-related event as described above will trigger an

interrupt if this bit is set to "1".

0 = SCSR-related event interrupt is disabled.

1 = SCSR-related event interrupt is enabled.