Rainbow Electronics W90P710CDG User Manual

Page 449

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 449 -

Revision B2

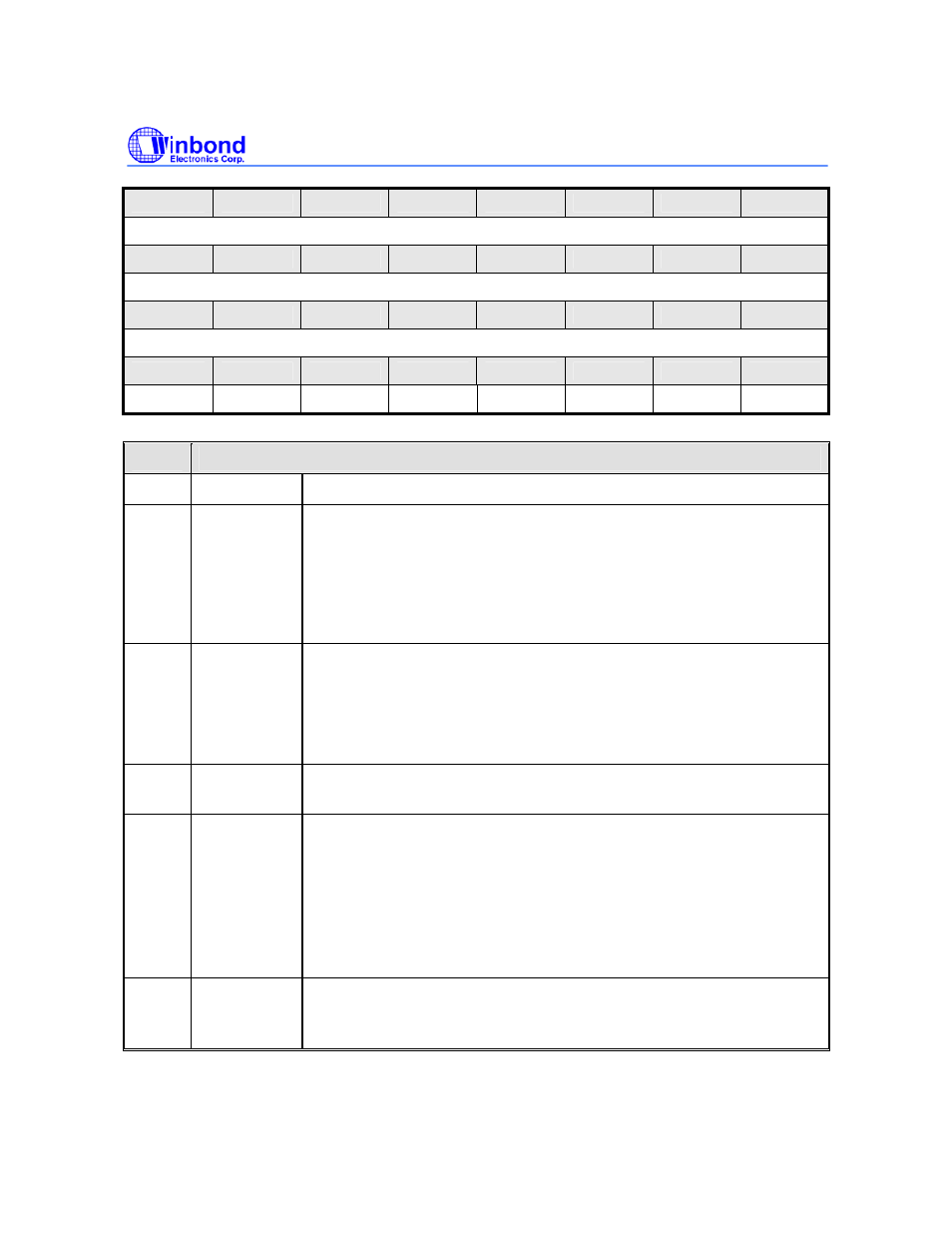

BITS

DESCRIPTIONS

[31:8]

RESERVED -

[7]

BDLAB

Baud rate Divisor Latch Access Bit.

When this bit is set to a logical "1", users may access baud rate divisor (in

16-bit binary format) through divisor latches (BLH and BLL) of baudrate

generator during a read/write operation. A special Smart Card ID can

also be read at base address + 8 when BDLAB is "1". When this bit is set

to "0", accesses to base address + 0, 4 or 8 refer to RBR/TBR, IER or

ISR/SCFR respectively.

[6]

DIR

DIRect convention

When set as a ‘0’ or ‘1’ will receive data in the direct convention or

indirect convention manner respectively. In other words, the controller will

need to have this bit set to a ‘1’ if the first byte of the ATR process is 3F

(i.e. Indirect convention) and a ‘0’ if the first byte is 3B (i.e. Direct

convention).

[5]

NSBE

Silent Byte Enable.

Receiver detect the data byte, parity bit and stop bit are all zero

[4]

EPE

Even Parity Enable.

This bit is only available when bit 3 of SCCR is programmed to "1". It

prescribes number of logical 1s in a data word including parity bit. When

this bit is set to "1", even parity is required for transmission and reception.

Odd parity is demanded when this bit is set to "0".

In contrast to its UART counterpart, Smart Card

Control Register only

controls parity bit setting because data length is fixed at 8-bit long for

Smart Card interface protocol.

[3]

Protocol

Protocol.

Bit PROT is set if the protocol is T = 1 (asynchronous) and bit PROT = 0 if

the protocol is T = 0.

31

30

29

28

27

26

25

24

RESERVED

23

22

21

20

19

18

17

16

RESERVED

15

14

13

12

11

10

9

8

RESERVED

7

6

5

4

3

2

1

0

BDLAB DIR NSBE EPE PROT CDP

Reserved

Reserved