Rainbow Electronics W90P710CDG User Manual

Page 536

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 537 -

Revision B2

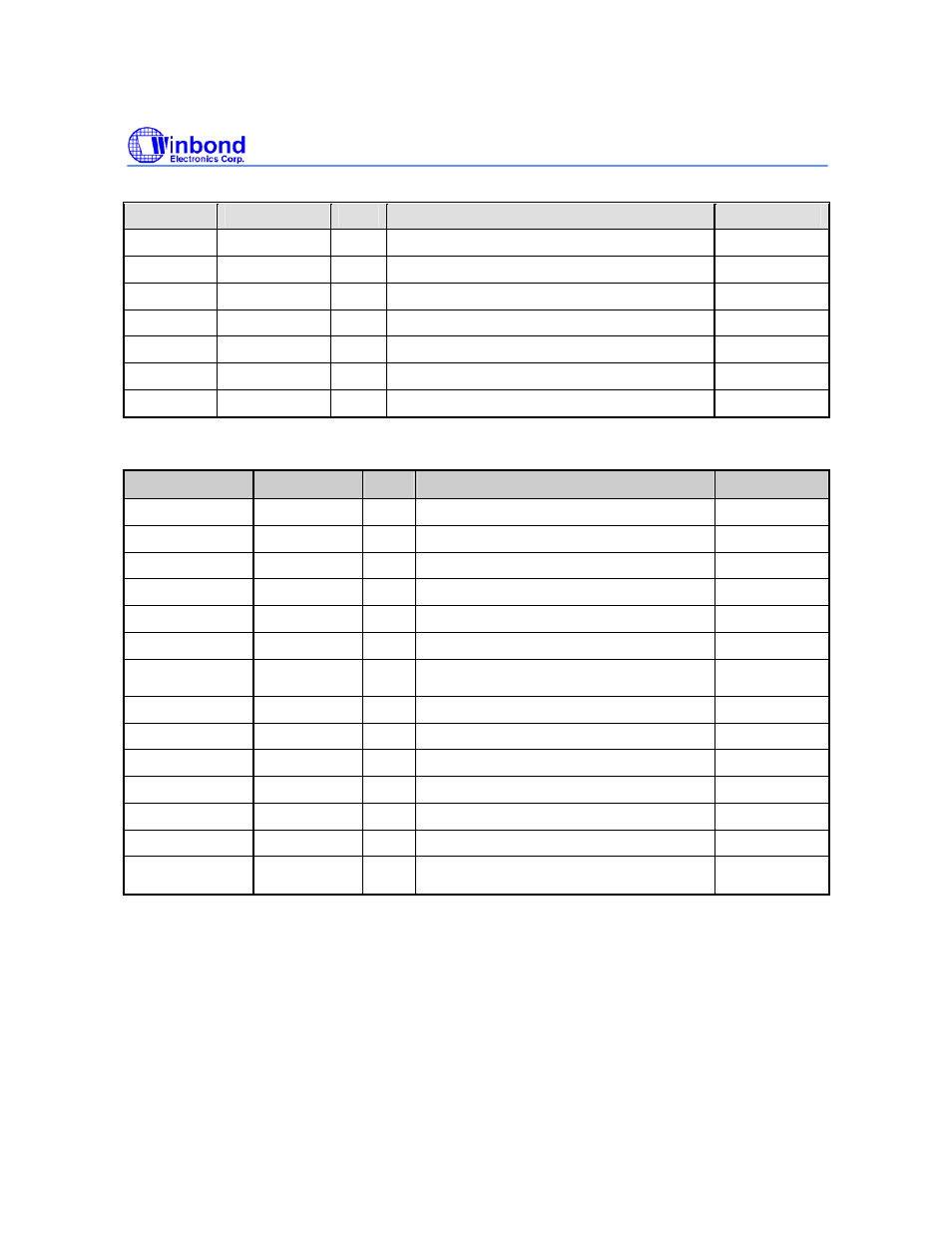

EMC Registers Map, continued

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

RXFSM 0xFFF0_3200

R

Receive

Finite

State Machine Register

0x0081_1101

TXFSM 0xFFF0_3204

R

Transmit Finite State Machine Register

0x0101_1101

FSM0 0xFFF0_3208

R

Finite

State Machine Register 0

0x0001_0101

FSM1 0xFFF0_320C

R

Finite

State Machine Register 1

0x1100_0100

DCR 0xFFF0_3210

R/W

Debug

Configuration Register

0x0000_003F

DMMIR

0xFFF0_3214

R

Debug Mode MAC Information Register

0x0000_0000

BISTR

0xFFF0_3300 R/W BIST Mode Register

0x0000_0000

GDMA Registers Map

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

GDMA_CTL0 0xFFF0_4000

R/W

Channel 0 Control Register

0x0000_0000

GDMA_SRCB0 0xFFF0_4004 R/W

Channel 0 Source Base Address Register

0x0000_0000

GDMA_DSTB0 0xFFF0_4008 R/W

Channel 0 Destination Base Address Register

0x0000_0000

GDMA_TCNT0 0xFFF0_400C R/W

Channel 0 Transfer Count Register

0x0000_0000

GDMA_CSRC0 0xFFF0_4010 R

Channel 0 Current Source Address Register

0x0000_0000

GDMA_CDST0 0xFFF0_4014 R

Channel 0 Current Destination Address Register

0x0000_0000

GDMA_CTCNT

0

0xFFF0_4018 R

Channel 0 Current Transfer Count Register

0x0000_0000

GDMA_CTL1 0xFFF0_4020

R/W

Channel 1 Control Register

0x0000_0000

GDMA_SRCB1 0xFFF0_4024 R/W

Channel 1 Source Base Address Register

0x0000_0000

GDMA_DSTB1 0xFFF0_4028 R/W

Channel 1 Destination Base Address Register

0x0000_0000

GDMA_TCNT1 0xFFF0_402C R/W

Channel 1 Transfer Count Register

0x0000_0000

GDMA_CSRC1 0xFFF0_4030 R

Channel 1 Current Source Address Register

0x0000_0000

GDMA_CDST1 0xFFF0_4034 R

Channel 1 Current Destination Address Register

0x0000_0000

GDMA_CTCNT

1

0xFFF0_4038 R

Channel 1 Current Transfer Count Register

0x0000_0000