Rainbow Electronics W90P710CDG User Manual

Page 477

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 477 -

Revision B2

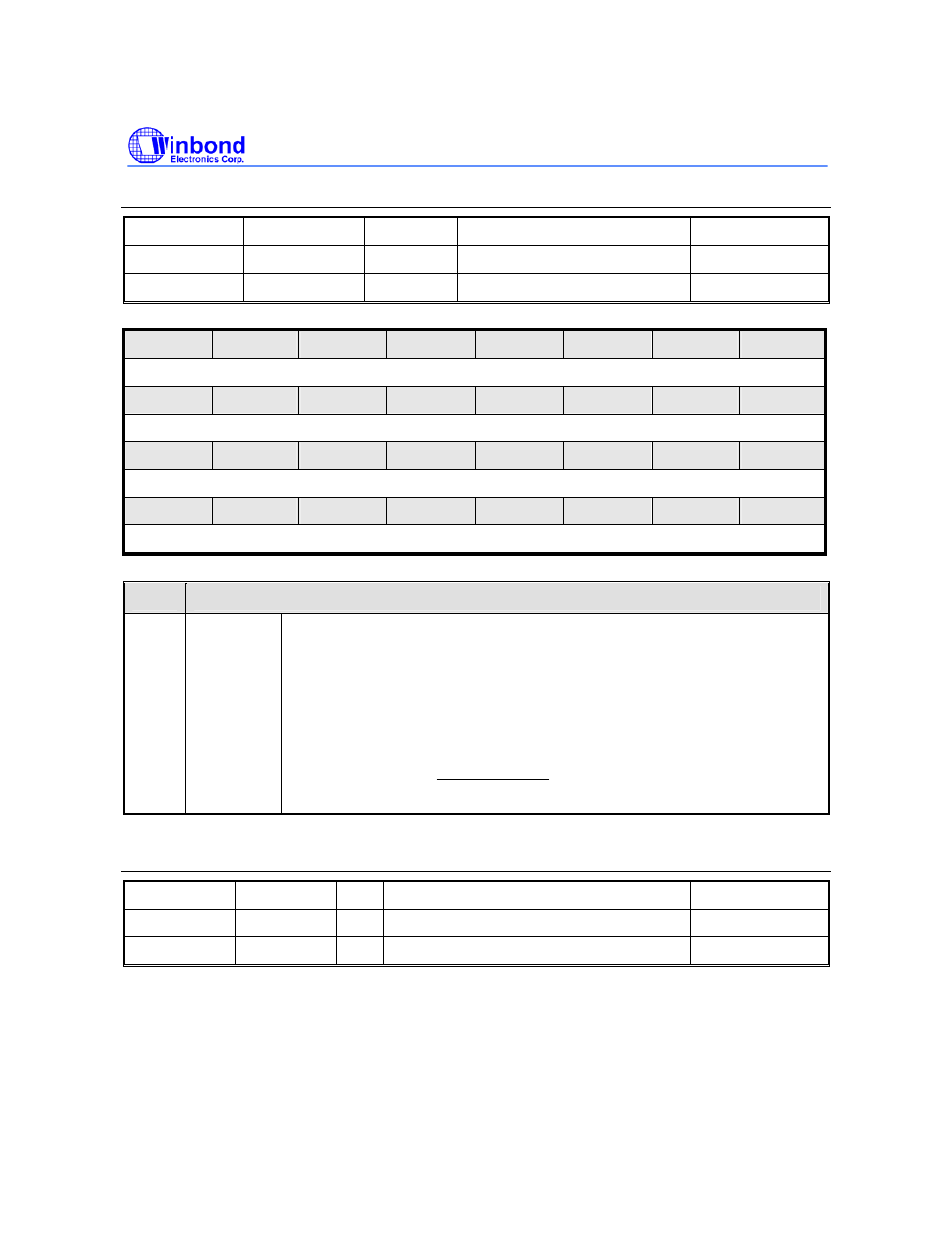

I2C Prescale Register 0/1 (I2C_DIVIDER 0 /1)

REGISTER ADDRESS R/W

DESCRIPTION

RESET

VALUE

I2C_DIVIDER0

0xFFF8_6004

R/W

I2C Clock Prescale Register 0

0x0000_0000

I2C_DIVIDER1

0xFFF8_6104

R/W

I2C Clock Prescale Register 1

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

DIVIDER[15:8]

7

6

5

4

3

2

1

0

DIVIDER[7:0]

BITS

DESCRIPTIONS

[15:0]

DIVIDER

Clock Prescale Register

It is used to prescale the SCL clock line. Due to the structure of the I

2

C

interface, the core uses a 5*SCL clock internally. The prescale register must

be programmed to this 5*SCL frequency (minus 1). Change the value of the

prescale register only when the “I2C_EN” bit is cleared.

Example: pclk = 32MHz, desired SCL = 100KHz

)

(

3

)

(

63

1

100

5

32

hex

F

dec

KHz

MHz

prescale

=

=

−

∗

=

I2C Command Register 0/1 (I2C_CMDR 0/1)

REGISTER ADDRESS

R/W

DESCRIPTION

RESET

VALUE

I2C_CMDR0

0xFFF8_6008

R/W

I2C Command Register 0

0x0000_0000

I2C_CMDR1

0xFFF8_6108

R/W

I2C Command Register 1

0x0000_0000