Rainbow Electronics W90P710CDG User Manual

Page 134

W90P710CD/W90P710CDG

- 134 -

Continued.

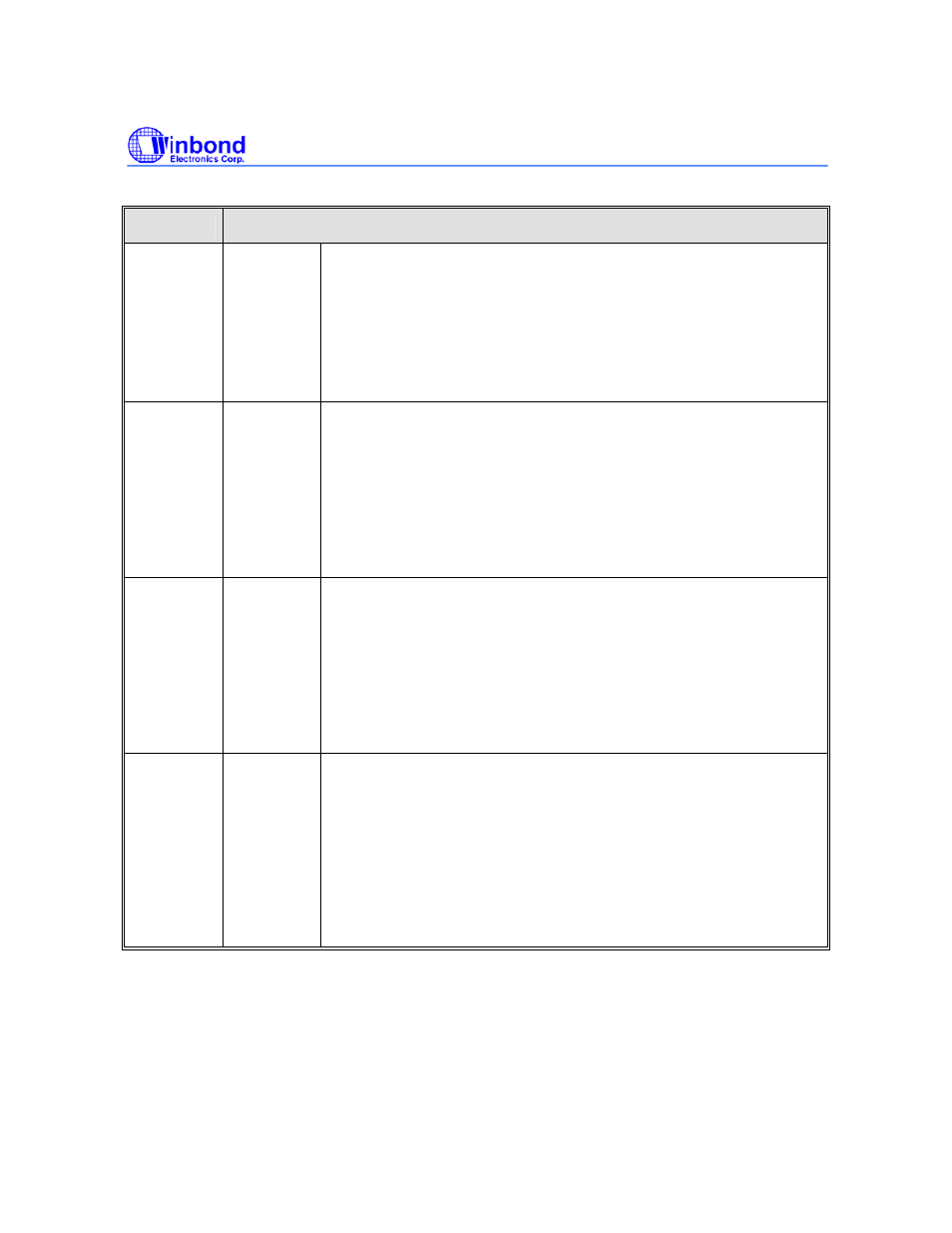

BITS

DESCRIPTIONS

[20] EnNCS

The Enable No Carrier Sense Interrupt controls the NCS interrupt

generation. If NCS of MISTA register is set, and both EnNCS and

EnTXINTR are enabled, the EMC generates the Tx interrupt to CPU. If

EnNCS or EnTXINTR is disabled, no Tx interrupt is generated to CPU

even the NCS of MISTA register is set.

1’b0: NCS of MISTA register is masked from Tx interrupt generation.

1’b1: NCS of MISTA register can participate in Tx interrupt generation.

[19] EnEXDEF

The Enable Defer Exceed Interrupt controls the EXDEF interrupt

generation. If EXDEF of MISTA register is set, and both EnEXDEF and

EnTXINTR are enabled, the EMC generates the Tx interrupt to CPU. If

EnEXDEF or EnTXINTR is disabled, no Tx interrupt is generated to

CPU even the EXDEF of MISTA register is set.

1’b0: EXDEF of MISTA register is masked from Tx interrupt generation.

1’b1: EXDEF of MISTA register can participate in Tx interrupt

generation.

[18] EnTXCP

The Enable Transmit Completion Interrupt controls the TXCP

interrupt generation. If TXCP of MISTA register is set, and both

EnTXCP and EnTXINTR are enabled, the EMC generates the Tx

interrupt to CPU. If EnTXCP or EnTXINTR is disabled, no Tx interrupt

is generated to CPU even the TXCP of MISTA register is set.

1’b0: TXCP of MISTA register is masked from Tx interrupt generation.

1’b1: TXCP of MISTA register can participate in Tx interrupt

generation.

[17] EnTXEMP

The Enable Transmit FIFO Underflow Interrupt controls the TXEMP

interrupt generation. If TXEMP of MISTA register is set, and both

EnTXEMP and EnTXINTR are enabled, the EMC generates the Tx

interrupt to CPU. If EnTXEMP or EnTXINTR is disabled, no Tx interrupt

is generated to CPU even the TXEMP of MISTA register is set.

1’b0: TXEMP of MISTA register is masked from Tx interrupt

generation.

1’b1: TXEMP of MISTA register can participate in Tx interrupt

generation.