Rainbow Electronics W90P710CDG User Manual

Page 131

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 131 -

Revision B2

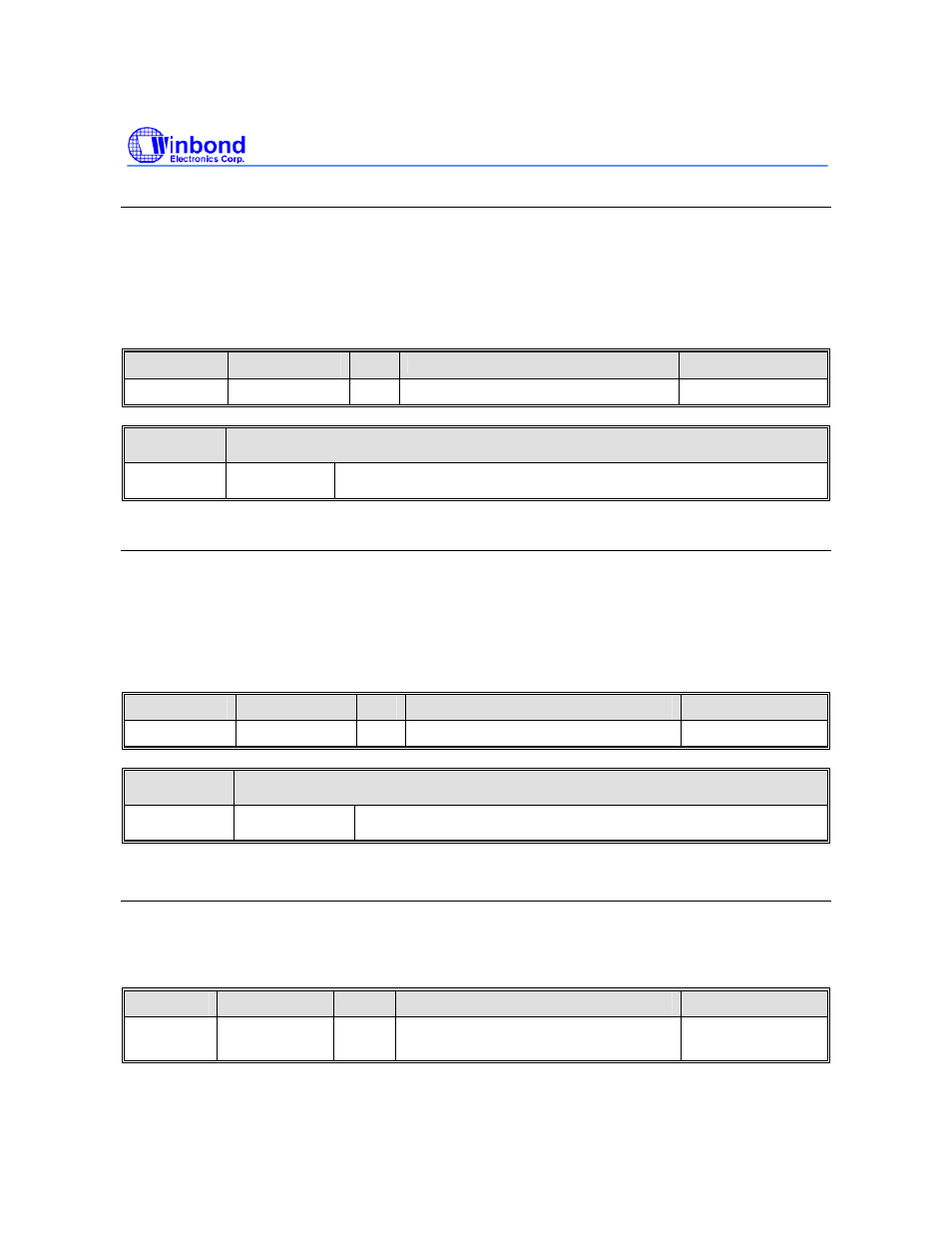

Transmit Start Demand Register (TSDR)

If the Tx descriptor is not available for use of TxDMA after the TXON of MCMDR register is enabled,

the FSM (Finite State Machine) of TxDMA enters the Halt state and the frame transmission is halted.

After the S/W has prepared the new Tx descriptor for frame transmission, it must issue a write

command to TSDR register to make TxDMA leave Halt state and contiguous frame transmission. The

TSDR is a write only register and read from this register is undefined. The write to TSDR register has

took effect only while TxDMA stayed at Halt state.

Register

Address

R/W

Description

Reset Value

TSDR

0xFFF0_30A0

W

Transmit Start Demand Register

Undefined

BITS

DESCRIPTIONS

[31:0] Reserved

-

Receive Start Demand Register (RSDR)

If the Rx descriptor is not available for use of RxDMA after the RXON of MCMDR register is enabled,

the FSM (Finite State Machine) of RxDMA enters the Halt state and the frame reception is halted.

After the S/W has prepared the new Rx descriptor for frame reception, it must issue a write command

to RSDR register to make RxDMA leave Halt state and contiguous frame reception. The RSDR is a

write only register and read from this register is undefined. The write to RSDR register has took effect

only while RxDMA stayed at Halt state.

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

RSDR 0xFFF0_30A4

W

Receive

Start Demand Register

Undefined

BITS

DESCRIPTIONS

[31:0] Reserved

--

Maximum Receive Frame Control Register (DMARFC)

The DMARFC defines the maximum frame length for a received frame that can be stored in the

system memory. It is recommend that only use this register while S/W wants to receive a frame which

length is greater than 1518 bytes.

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

DMARFC 0xFFF0_30A8 R/W

Maximum Receive Frame Control

Register

0x0000_0800