Rainbow Electronics W90P710CDG User Manual

Page 70

W90P710CD/W90P710CDG

- 70 -

Continued.

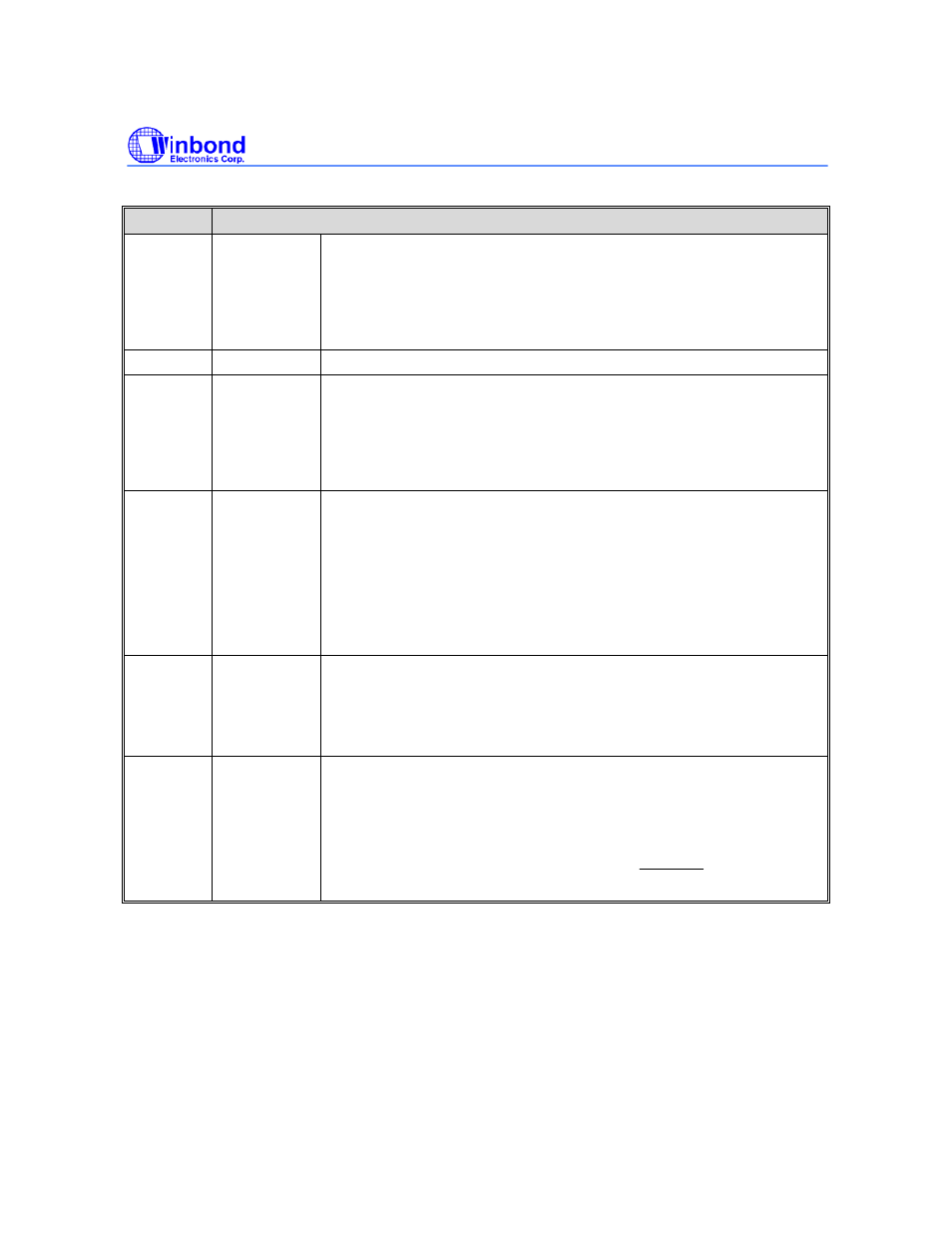

BITS

DESCRIPTION

[24] EXBE0

External IO bank 0 byte enable

This bit function description is the same as EXBE3 above.

1 = nWBE[3:0] pin is byte enable signals, nWE will be used as write

strobe signal to SRAM

0 = nWBE[3:0] pin is byte write strobe signal

[23:19] RESERVED

[18] REFEN

Enable SDRAM refresh cycle for SDRAM bank0 & bank1

This bit set will start the auto-refresh cycle to SDRAM. The refresh rate is

according to REFRAT bits.

1 = Enable refresh function

0 = Disable refresh function

[17] REFMOD

Refresh mode of SDRAM for SDRAM bank

Defines the refresh mode type of external SDRAM bank

Software can write this bit “1” to force SDRAM enter self-refresh mode.

0 = Auto refresh mode

1 = Self refresh mode

NOTE: If any read/write to SDRAM occurs then this bit will be cleared to

“0” by hardware automatically and SDRAM will enter auto-refresh mode.

[16] CLKEN

Clock enable for SDRAM

Enables the SDRAM clock enable (CKE) control signal

0 = Disable (power down mode)

1 = Enable (Default)

[15:3] REFRAT

Refresh count value for SDRAM

The SDRAM Controller automatically provides an auto refresh cycle for

every refresh period programmed into the REFRAT bits when the

REFEN bit of each bank is set

The refresh period is calculated as

fMCLK

value

period

=