Rainbow Electronics W90P710CDG User Manual

Page 91

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 91 -

Revision B2

The unlock all operation is used to unlock the whole D-Cache. This operation is performed on all cache

lines. In case a line is locked, it is unlocked and starts to operate as regular valid cache line. In case a

line is not locked or if it is invalid, no operation is performed. To unlock the whole cache, set the ULKA

and DCAH bits.

6.4.5 Write

Buffer

The W90P710 provides a write buffer to improve system performance. The write buffer can buffer up to

eight words of data. The write buffer may be enabled or be disabled via the WRBEN bit in the CAHCNF

register, and the buffer is disabled and flushed on reset.

Drain write buffer

To force data, this is in write buffer, to be written to external main memory. This operation is useful in real

time applications where the processor needs to be sure that a write to a peripheral has completed before

program execution continues.

To perform this command, you can set the DRWB and DCAH bits in CAHCON register.

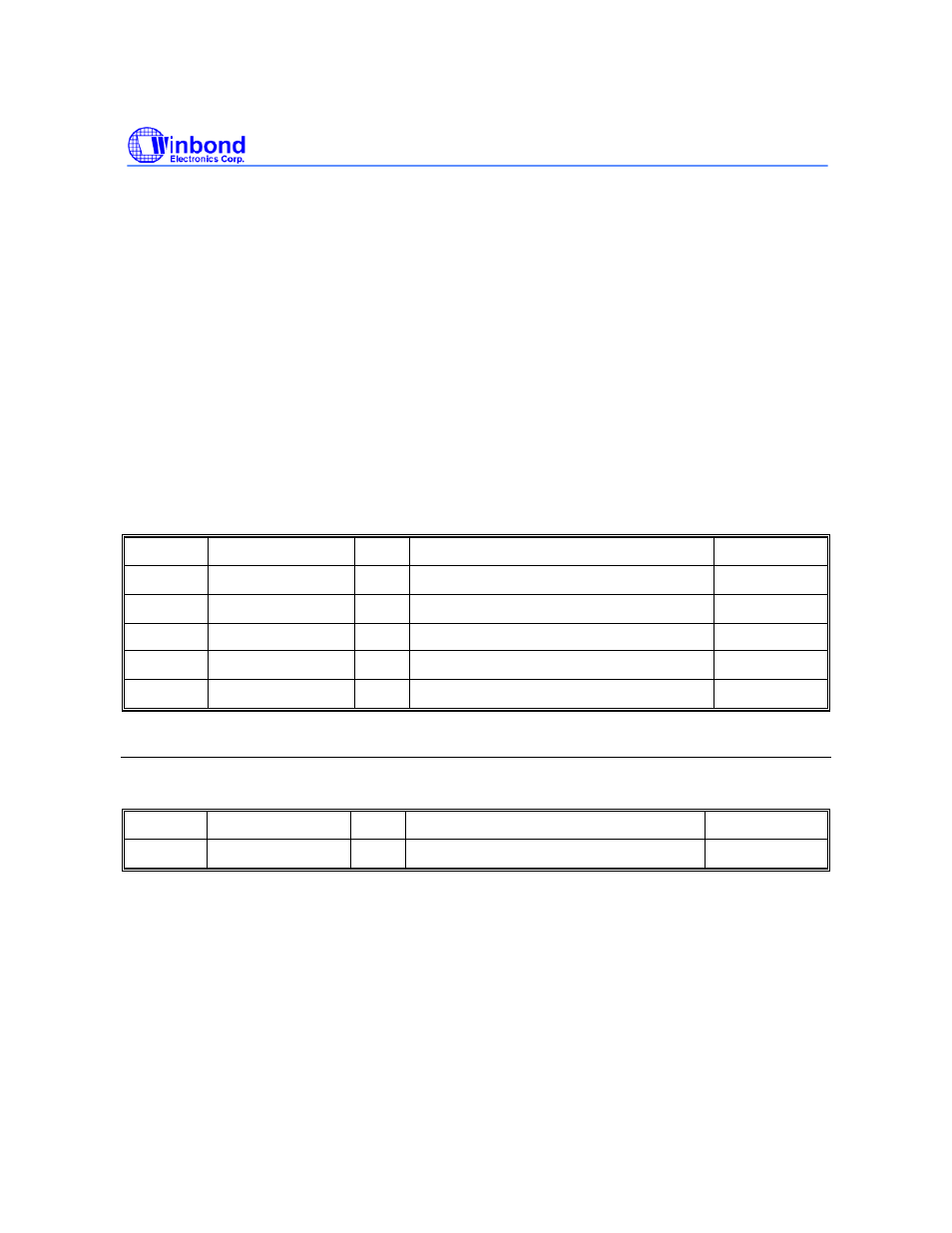

6.4.6 Cache Control Registers Map

REGISTER ADDRESS R/W

DESCRIPTION

RESET

VALUE

CAHCNF

0xFFF0_2000

R/W Cache configuration register

0x0000_0000

CAHCON

0xFFF0_2004

R/W Cache control register

0x0000_0000

CAHADR 0xFFF0_2008 R/W Cache

address register

0x0000_0000

CTEST0

0xFFF6_0000

R/W Cache test register 0

0x0000_0000

CTEST1

0xFFF6_0004

R

Cache test register 1

0x0000_0000

Configuration Register (CAHCNF)

Cache controller has a configuration register to enable or disable the I-Cache, D-Cache, and Write

buffer.

REGISTER ADDRESS R/W

DESCRIPTION

RESET

VALUE

CAHCNF

0xFFF0_2000

R/W Cache configuration register

0x0000_0000