Rainbow Electronics W90P710CDG User Manual

Page 271

W90P710CD/W90P710CDG

Publication Release Date: September 19, 2006

- 271 -

Revision B2

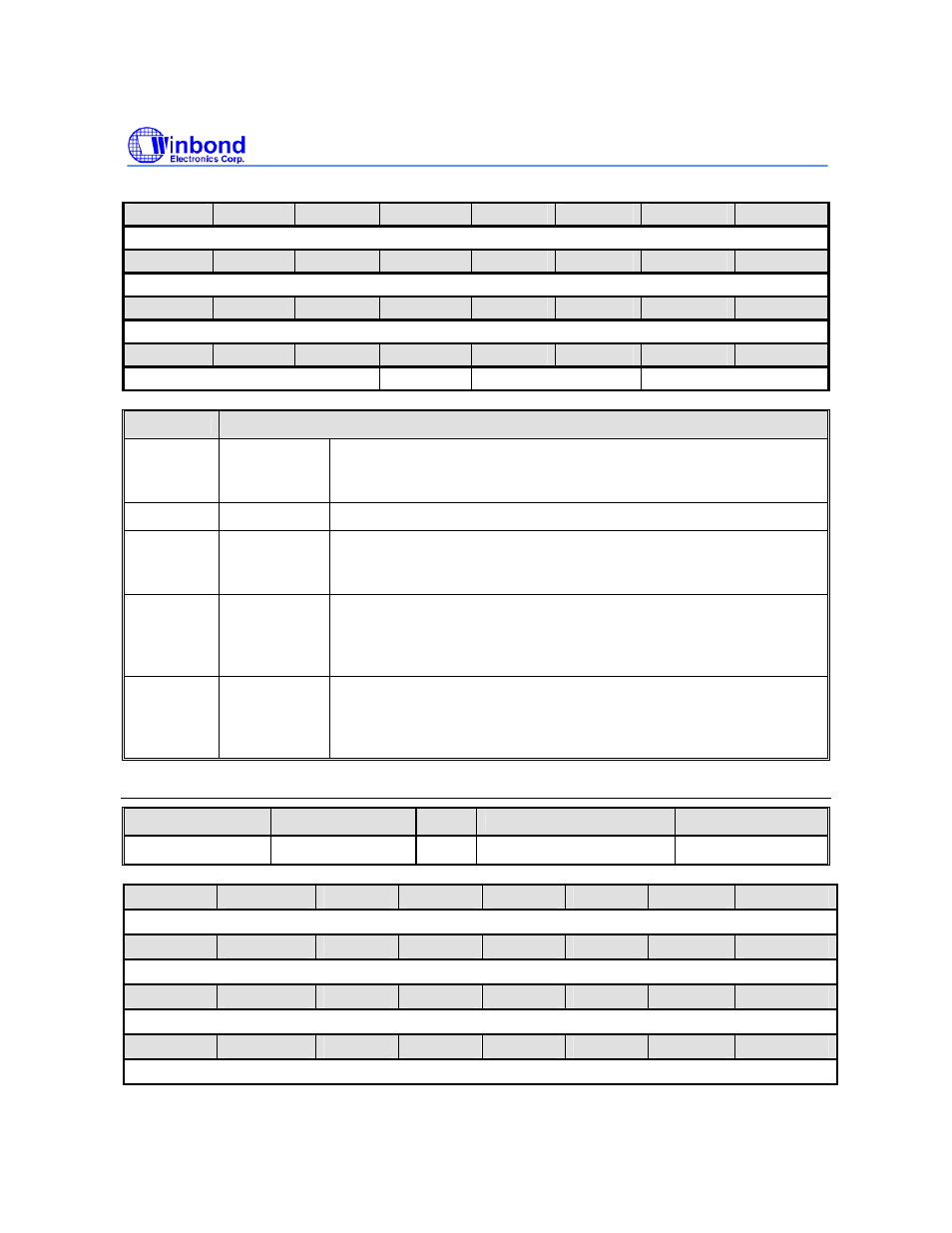

31

30

29

28

27

26

25

24

F2STRIDE[15:8]

23

22

21

20

19

18

17

16

F2STRIDE[7:0]

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

Reserved F2LOCK

F2BURSTY

F2TRANSZ

BITS

DESCRIPTIONS

[31:16] F2STRIDE

Video frame buffer stride

16-bit value specifies the word offset of memory address of vertically

adjacent line for FIFO2 fetching.

[15:5] Reserved Reserved

[4] F2LOCK

FIFO2 lock transfer enable

0 = Disable

1 = Enable

[3:2] F2BURSTY

FIFO2 burst transfer type

00 =4 data burst mode

01 =8 data burst mode

10 =16 data burst mode

[1:0] F2TRANSZ

FIFO2 data width per-transfer

00=one byte

01=half word

10=one word

FIFO1 Start Address Register (FIFO1SADDR)

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

FIFO1SADDR

0xFFF0_8030

R/W

FIFO1 start address

0x0000_0000

31

30

29

28

27

26

25

24

FIFO1SADDR[31:24]

23

22

21

20

19

18

17

16

FIFO1SADDR[23:16]

15

14

13

12

11

10

9

8

FIFO1SADDR[15:8]

7

6

5

4

3

2

1

0

FIFO1SADDR[7:0]