Rainbow Electronics W90P710CDG User Manual

Page 350

W90P710CD/W90P710CDG

- 350 -

6.12.6 High speed UART Controller

The High Speed Universal Asynchronous Receiver/Transmitter (HS_UART) performs a serial-to-

parallel conversion on data characters received from the peripheral, and a parallel-to-serial conversion

on data characters received from the CPU. There are five types of interrupts, they are, transmitter

FIFO empty interrupt, receiver threshold level reaching interrupt, line status interrupt (overrun error or

parity error or framing error or break interrupt) ,time out interrupt, and Modem status interrupt . One

64-byte transmitter FIFO (TX_FIFO) and one 64-byte (plus 3-bit of error data per byte) receiver FIFO

(RX_FIFO) has been built in to reduce the number of interrupts presented to the CPU. The CPU can

completely read the status of the UART at any time during the operation. The reported status

information includes the type and condition of the transfer operations being performed by the UART,

as well as any error conditions (parity, overrun, framing, or break interrupt) found. The UART includes

a programmable baud rate generator that is capable of dividing crystal clock input by divisors to

produce the clock that transmitter and receiver needed. The equation is

Baud Out = crystal clock / 16 * [Divisor + 2].

The UART includes the following features:

y

Transmitter and receiver are buffered with a 64-byte FIFO each to reduce the number of

interrupts presented to the CPU.

y

Subset of MODEM control function(selected by IP)

y

Fully programmable serial-interface characteristics:

¾

5-, 6-, 7-, or 8-bit character

¾

Even, odd, or no-parity bit generation and detection

¾

1-, 1&1/2, or 2-stop bit generation

¾

Baud rate generation

y

False start bit detection

y

Full-prioritized interrupt system controls

y

Not support Loop back mode

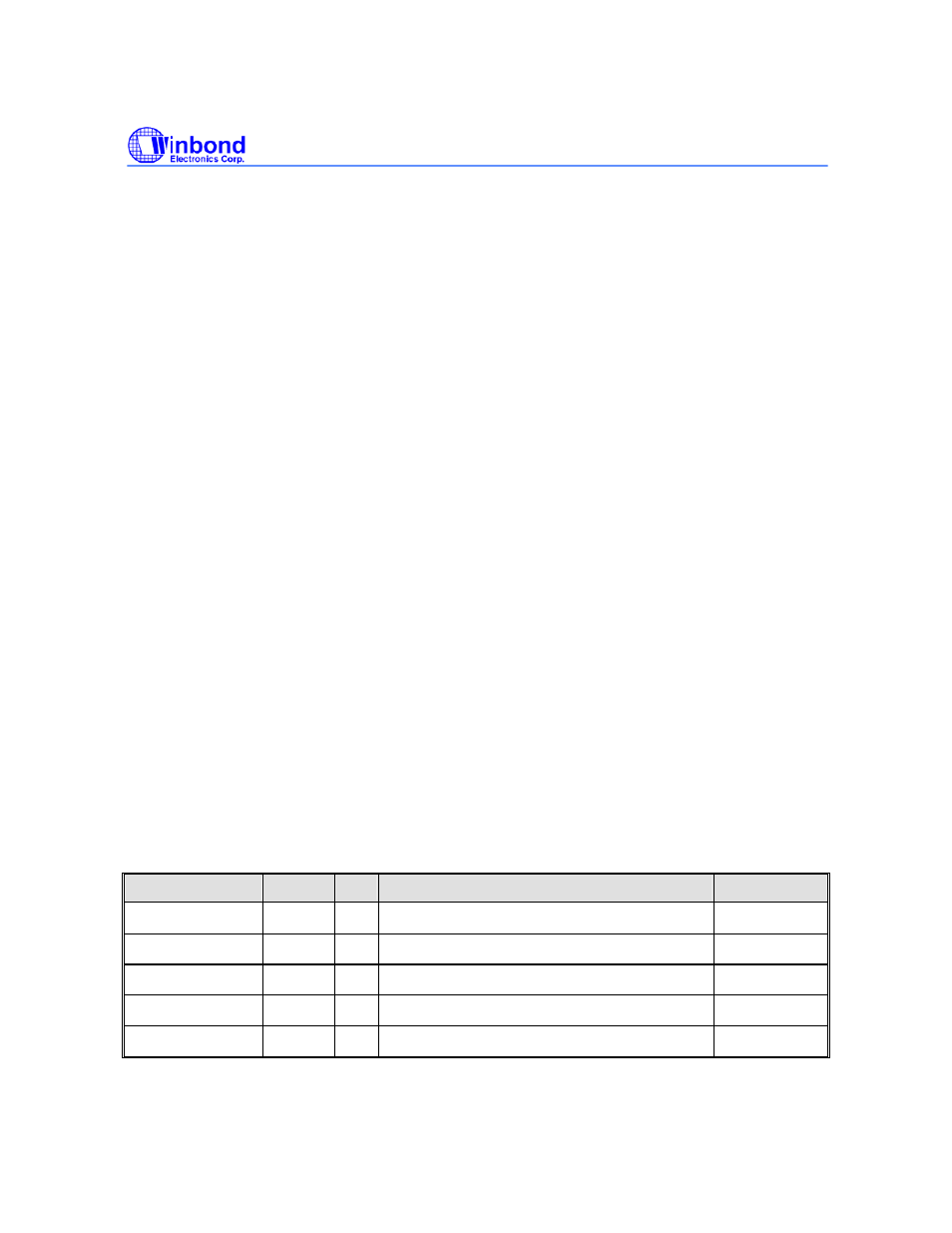

6.12.6.1 High Speed UART Control Registers Map

R: read only, W: write only, R/W: both read and write, C: Only value 0 can be written

REGISTER

OFFSET R/W

DESCRIPTION

RESET VALUE

HSUART_RBR 0x00

R

Receive

Buffer

Register (DLAB = 0)

Undefined

HSUART_THR 0x00

W

Transmit

Holding

Register (DLAB = 0)

Undefined

HSUART_IER 0x04

R/W

Interrupt

Enable Register (DLAB = 0)

0x0000_0000

HSUART_DLL 0x00

R/W

Divisor

Latch

Register (LS)(DLAB = 1)

0x0000_0000

HSUART_DLM 0x04

R/W

Divisor Latch Register (MS)(DLAB = 1)

0x0000_0000