FUJITSU MB91F109 FR30 User Manual

Page 94

70

CHAPTER 2 CPU

■

Mode Data

Data that the CPU writes at 0000 07FF

H

after resetting is called mode data.

The mode register (MODR) exists at 0000 07FF

H

. After mode data is set to this register, the

CPU operates based on the mode set to the register.

Mode data can be written to the mode register only once after resetting. The mode set to the

register is validated immediately after it is set.

■

Mode Register (MODR)

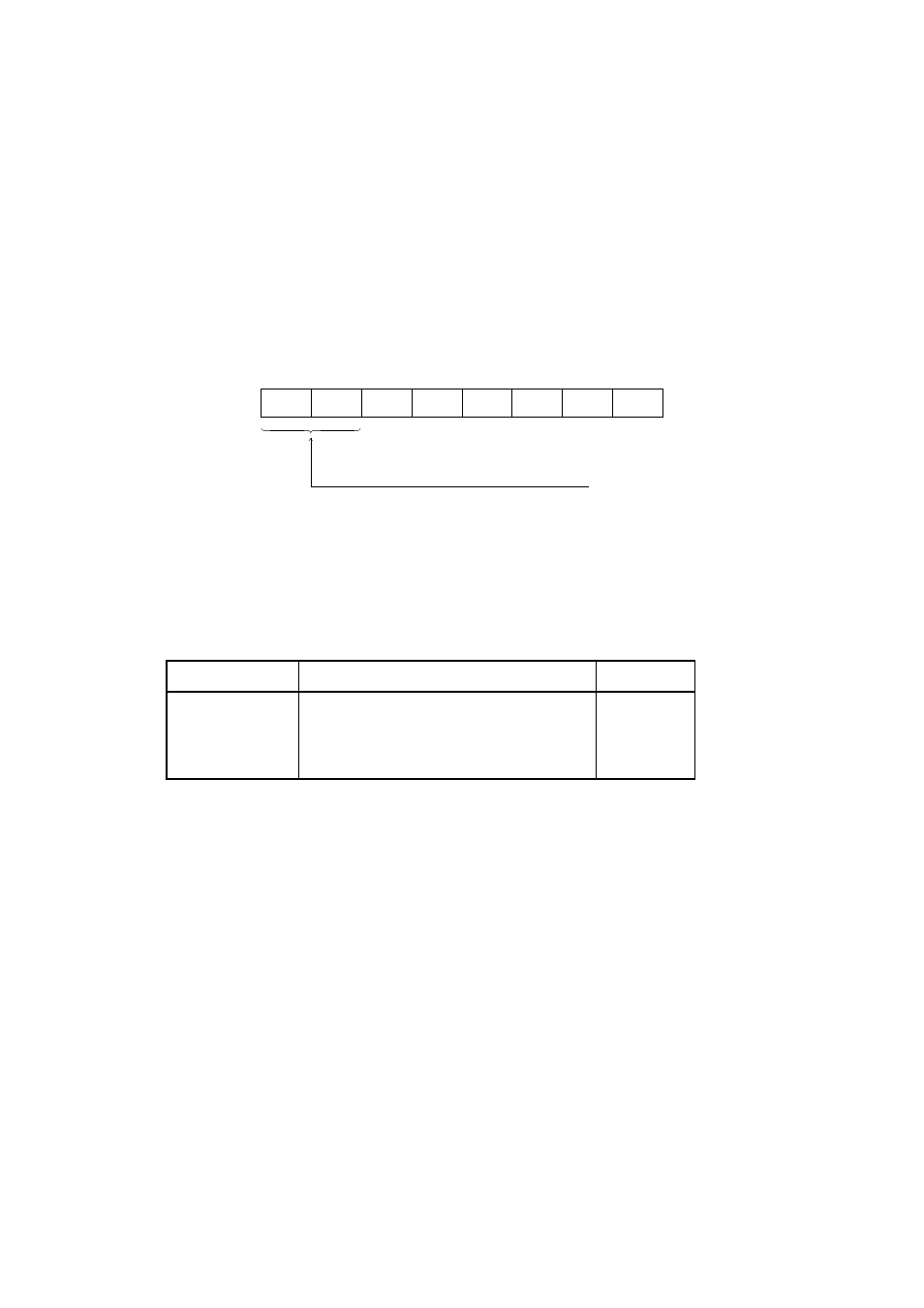

Figure 2.10.1 shows the configuration of the mode register (MODR).

Figure 2.10-1 Mode Register Configuration

❍

Bus mode setting bits (M1, M0)

These bits specify the bus mode that becomes valid after completion of writing to the mode

register.

Table 2.10.2 summarizes the functions that can be specified by combinations of these bits.

Set only "10" for a model that has no internal ROM.

❍

Other bits (*)

Always write 0 to these bits.

■

Notes on Writing to the Mode Register (MODR)

Before writing to the MODR, be sure to set AMD0 to AMD5 to decide the bus width of each chip

select (CS) area.

The MODR has no bits used to set the bus width.

For a bus width, the value set to mode pins MD2 to MD0 is valid before writing to the MODR,

and the value set to BW1 and BW0 of AMD0 to AMD5 is valid after writing to the MODR.

For instance, external reset vectors are normally processed in the normal area 0 (in which

CS0X is active) and the bus width for this operation is determined by the MD2 to MD0 pins. If a

bus width of 16 bits is set to MD2 to MD0, and the MODR is written without writing to AMD0,

area 0 shifts to an 8-bit bus mode after writing to the MODR. This is because the default bus

width of AMD0 is 8 bits, and consequently causes a malfunction.

To prevent this problem, be sure to set AMD0 to AMD5 before writing to the MODR.

Initial value

MODR address: 0000 07FF

H

M1

M0

*

*

*

*

*

*

XXXXXXXX

W

Bus mode setting bits

Access

Table 2.10-2 Bus Mode Setting Bit and the Function

M1

M0

Function

Remarks

0

0

1

1

0

1

0

1

Single chip mode

Internal-ROM-external bus mode

External-ROM-external bus mode

-

Reserved