FUJITSU MB91F109 FR30 User Manual

Page 435

411

APPENDIX E Instructions

■

Logical Operation Instructions

■

Bit Operation Instructions

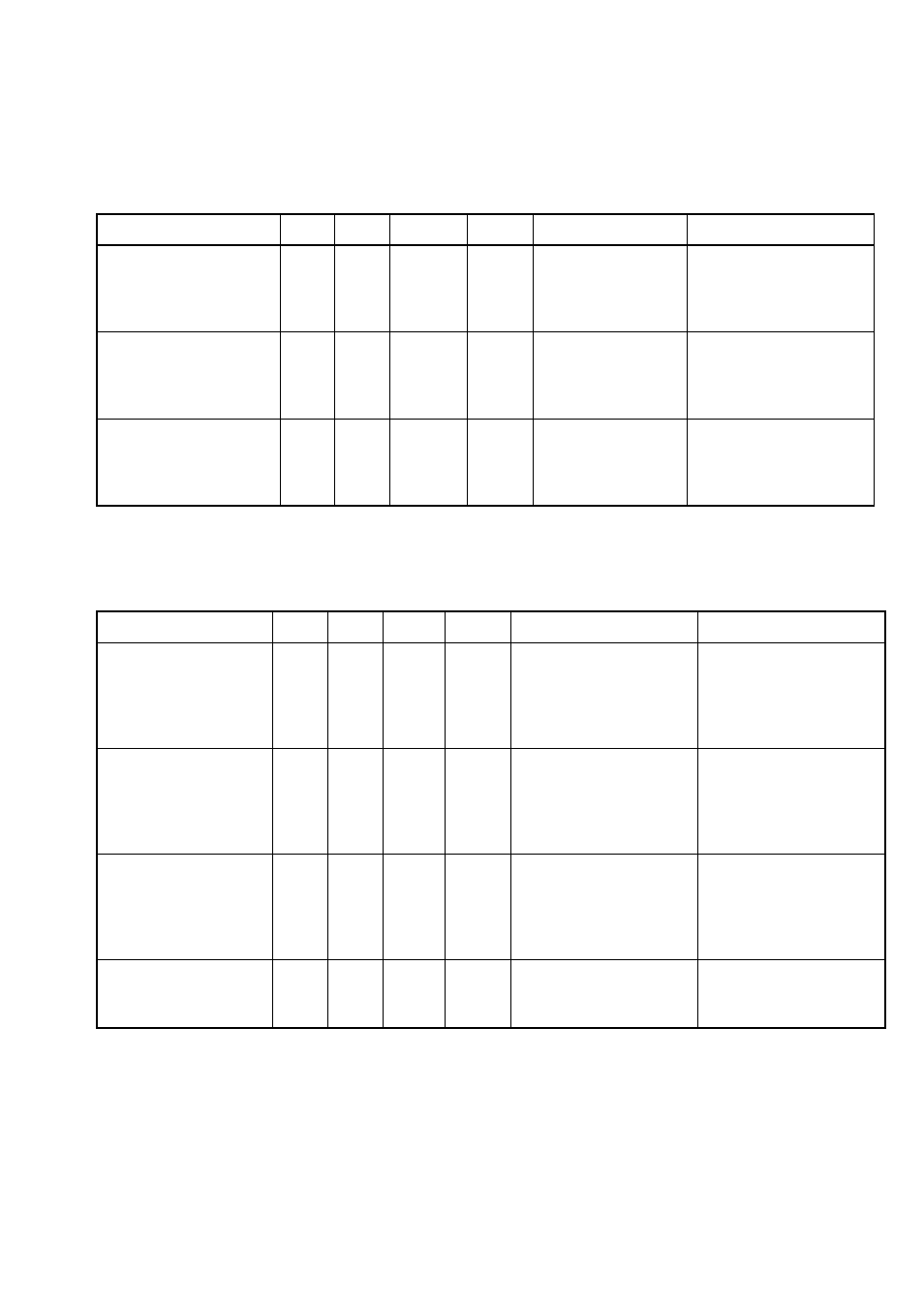

Table E.1-3 Logical Operation Instructions

Mnemonic

Type

OP

Cycle

NZVC

Operation

Remarks

AND

Rj, Ri

AND

Rj, @Ri

ANDH Rj, @Ri

ANDB Rj, @Ri

A

A

A

A

82

84

85

86

1

1+2a

1+2a

1+2a

CC--

CC--

CC--

CC--

Ri &= Rj

(Ri) &= Rj

(Ri) &= Rj

(Ri) &= Rj

Word

Word

Half-word

Byte

OR

Rj, Ri

OR

Rj, @Ri

ORH

Rj, @Ri

ORB

Rj, @Ri

A

A

A

A

92

94

95

96

1

1+2a

1+2a

1+2a

CC--

CC--

CC--

CC--

Ri |= Rj

(Ri)|= Rj

(Ri)|= Rj

(Ri)|= Rj

Word

Word

Half-word

Byte

EOR

Rj, Ri

EOR

Rj, @Ri

EORH Rj, @Ri

EORB Rj, @Ri

A

A

A

A

9A

9C

9D

9E

1

1+2a

1+2a

1+2a

CC--

CC--

CC--

CC--

Ri ^= Rj

(Ri)^= Rj

(Ri)^= Rj

(Ri)^= Rj

Word

Word

Half-word

Byte

Table E.1-4 Bit Operation Instructions

Mnemonic

Type

OP

Cycle

NZVC

Operation

Remarks

BANDL #u4, @Ri

BANDH #u4, @Ri

*BAND #u8, @Ri*

1

C

C

80

81

1+2a

1+2a

----

----

----

(Ri)&=(0xF0+u4)

(Ri)&=((u4<<4)+0x0F

H

)

(Ri)&=u8

Lower 4 bits are subject

to operation.

Upper 4 bits are subject

to operation.

BORL

#u4, @Ri

BORH #u4, @Ri

*BOR

#u8, @Ri*

2

C

C

90

91

1+2a

1+2a

----

----

----

(Ri)|= u4

(Ri)|= (u4<<4)

(Ri)|= u8

Lower 4 bits are subject

to operation.

Upper 4 bits are subject

to operation.

BEORL #u4, @Ri

BEORH #u4, @Ri

*BEOR #u8, @Ri*

3

C

C

98

99

1+2a

1+2a

----

----

----

(Ri)^= u4

(Ri)^= (u4<<4)

(Ri)^= u8

Lower 4 bits are subject

to operation.

Upper 4 bits are subject

to operation.

BTSTL #u4, @Ri

BTSTH#u4, @Ri

C

C

88

89

2+a

2+a

0C--

CC--

(Ri) & u4

(Ri) & (u4<<4)

Lower 4-bit test

Upper-4 bit test

*1

The assembler creates BANDL if the bit is ON in u8&0x0F and BANDH if the bit is ON in u8&0xF0.

Both BANDL and BANDH may be created.

*2

The assembler creates BORL if the bit is ON in u8&0x0F and BORH if the bit is ON in u8&0xF0.

Both BORL and BORH may be created.