FUJITSU MB91F109 FR30 User Manual

Page 415

391

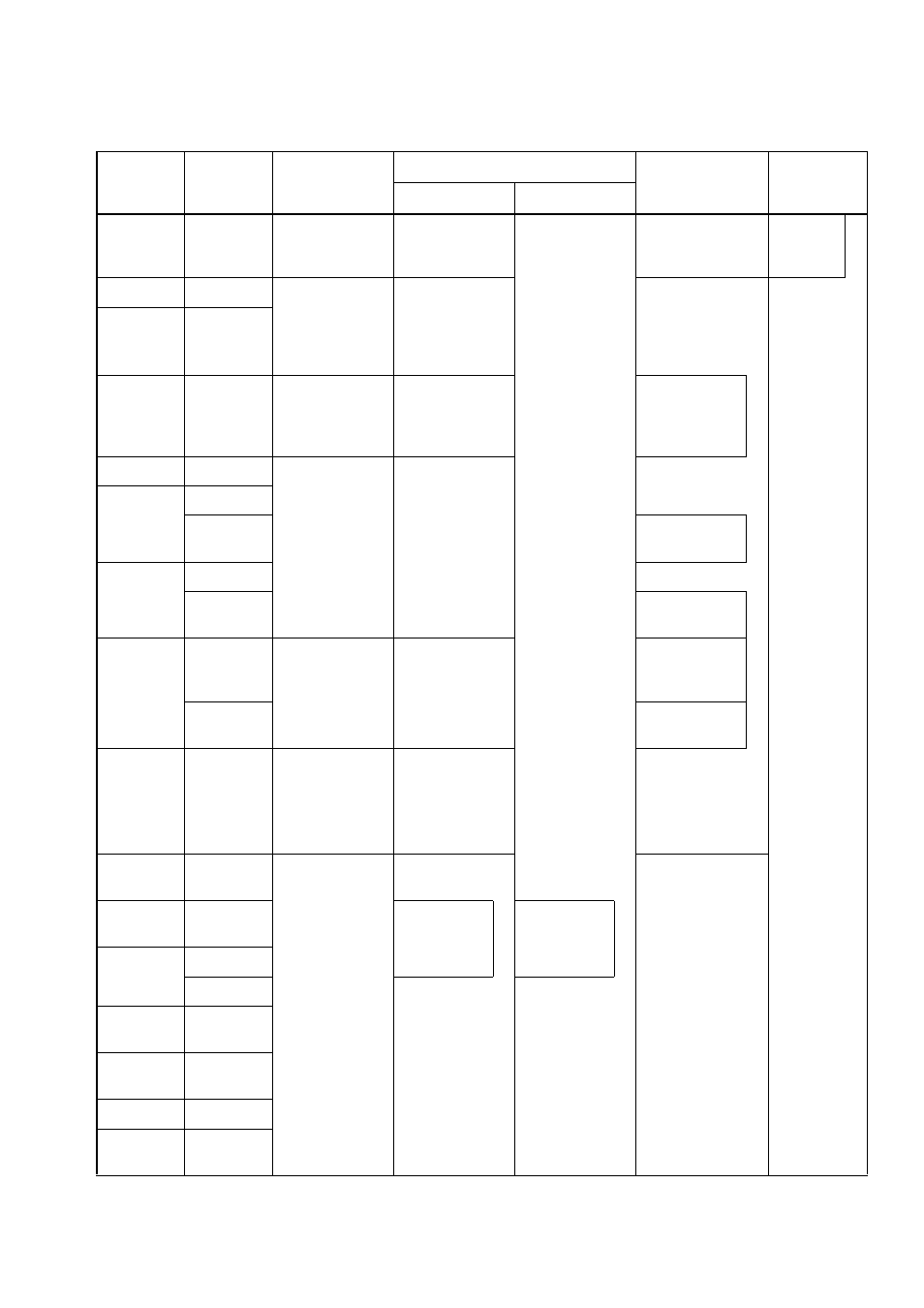

APPENDIX C Pin Status for Each CPU Status

PA6

CLK

P: Previous

status retained

F: CLK output

P, F: Previous

status retained

Output Hi-Z/

Input fixed to 0

CLK Output

CLK

Output

PB0

RAS0

P: Previous

status retained

F: Previous

value retained

(*2)

Same as left

during refresh

(*1)

P: Previous

status retained

F: Previous value

retained (*2)

Output Hi-Z/

Input

allowed for

all pins

PB1

CS0L

PB2

CS0H

P: Previous

status retained

F: Previous

value retained

P: Previous

status retained

F: Previous

value retained

Previous

status

retained

PB3

DW0X

P: Previous

status retained

F: Previous

value retained

(*2)

Same as left

during refresh

(*1)

PB4

RAS1

EOP2

Previous

value retained

PB5

CS1L

DREQ2

Previous

value retained

PB6

CS1H

P: Previous

status retained

F: Previous

value retained

P: Previous

status retained

F: Previous

value retained

Previous

status

retained

DACK2

Previous

value retained

PB7

DW1X

P: Previous

status retained

F: Previous

value retained

(*2)

Same as left

during refresh

(*1)

AN0 to

AN3

AN0-3

Previous status

retained

Previous status

retained

PE0 to

PE2

INT0-INT2

Input

possible

Input

possible

PE3

INT3

SC2

Previous status

retained

PE4 to

PE5

DREQ0-

DREQ1

PE6 to

PE7

DACK0-

DACK1

PF0

SI0, TRG0

PF1

SO0,

TRG1

Table C-4 Pin Status in 8-bit External Bus Mode (Continued)

Pin name

Function

During sleep

During stop

Bus release

(BGRNT)

Reset time

HIZX=0

HIZX=1