FUJITSU MB91F109 FR30 User Manual

Page 100

76

CHAPTER 3 CLOCK GENERATOR AND CONTROLLER

3.2

Reset Reason Resister (RSRR) and Watchdog Cycle

Control Register (WTCR)

The reset reason register (RSRR) holds the type of the reset event that occurred, and

the watchdog cycle control register (WTCR) specifies the cycle of the watchdog timer.

■

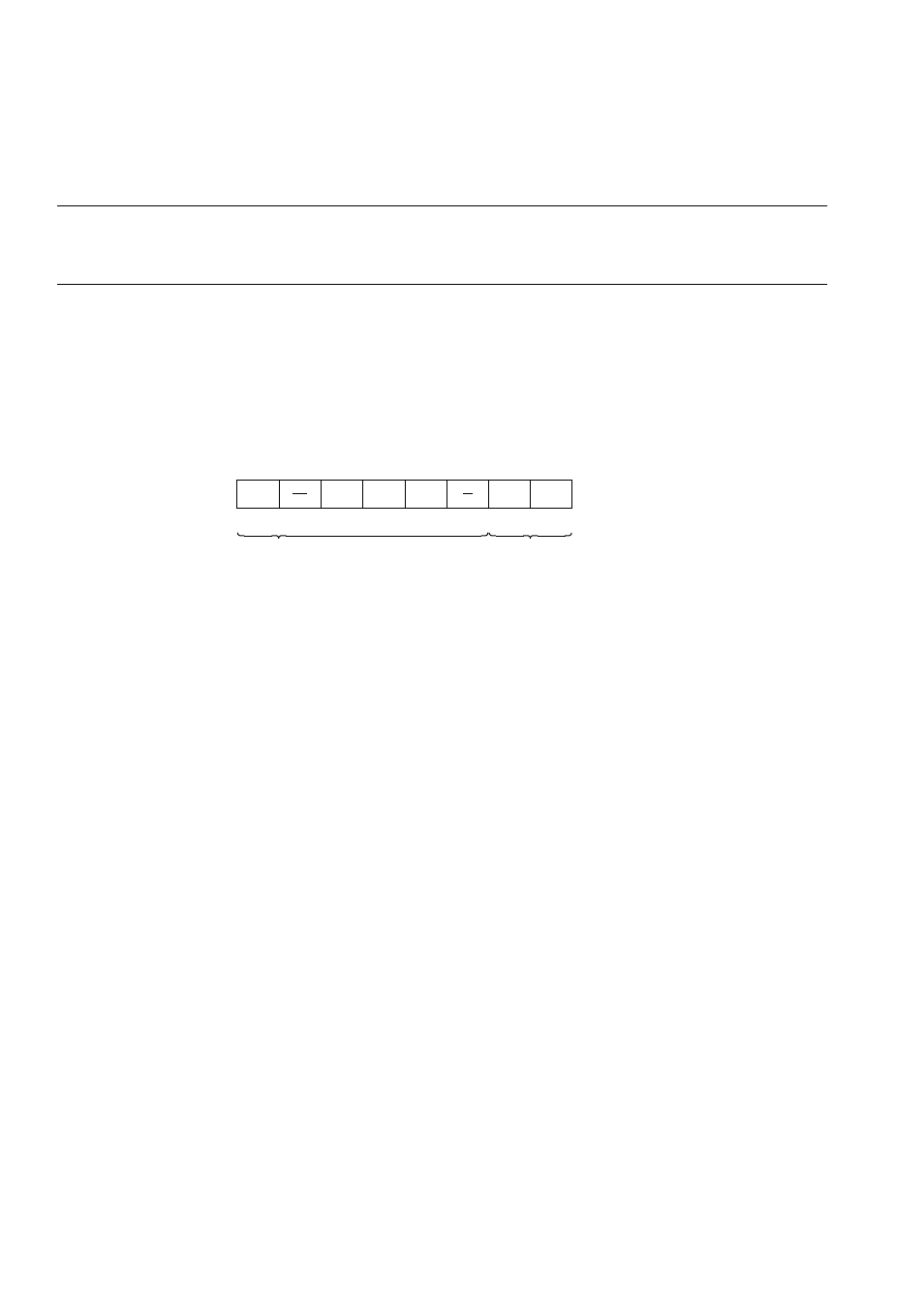

Configuration of Reset Reason Register (RSRR) and Watchdog Cycle Control Register (WTCR)

The configuration of the reset reason register (RSRR) and watchdog cycle control register

(WTCR) is shown below:

■

Bit Functions of the Reset Reason Register (RSRR) and Watchdog Cycle Control Register (WTCR)

[bit 15] PONR

When "1", the bit indicates that the reset that occurred previously was a power-on reset. It

also indicates that the other bits of this register are invalid.

[bit 14] (Reserved)

This bit is reserved. The value read from this bit undefined.

[bit 13] WDOG

When "1", the bit indicates that the reset that occurred previously was a watchdog reset.

[bit 12] ERST

When "1", the bit indicates that the reset that occurred previously was a reset caused by the

external reset pin.

[bit 11] SRST

When "1", the bit indicates that the reset that occurred previously was a reset caused by a

software reset request.

[bit 10] (Reserved)

This bit is reserved. The value read from this bit undefined.

15

14

13

12

11

10

09

08

00000480

H

PONR

WDOG ERST SRST

WT1 WT0

1XXXX-00

R/W

RSRR(R)

WTCR(W)

After power-on

Initial value

Access