FUJITSU MB91F109 FR30 User Manual

Page 357

333

15.5 Descriptor Register in RAM

[bits 5, 4] DCS1, DCS0: Transfer destination address update mode

These bits specify the mode in which the transfer source or destination address is updated

each time DMA transfer is performed.

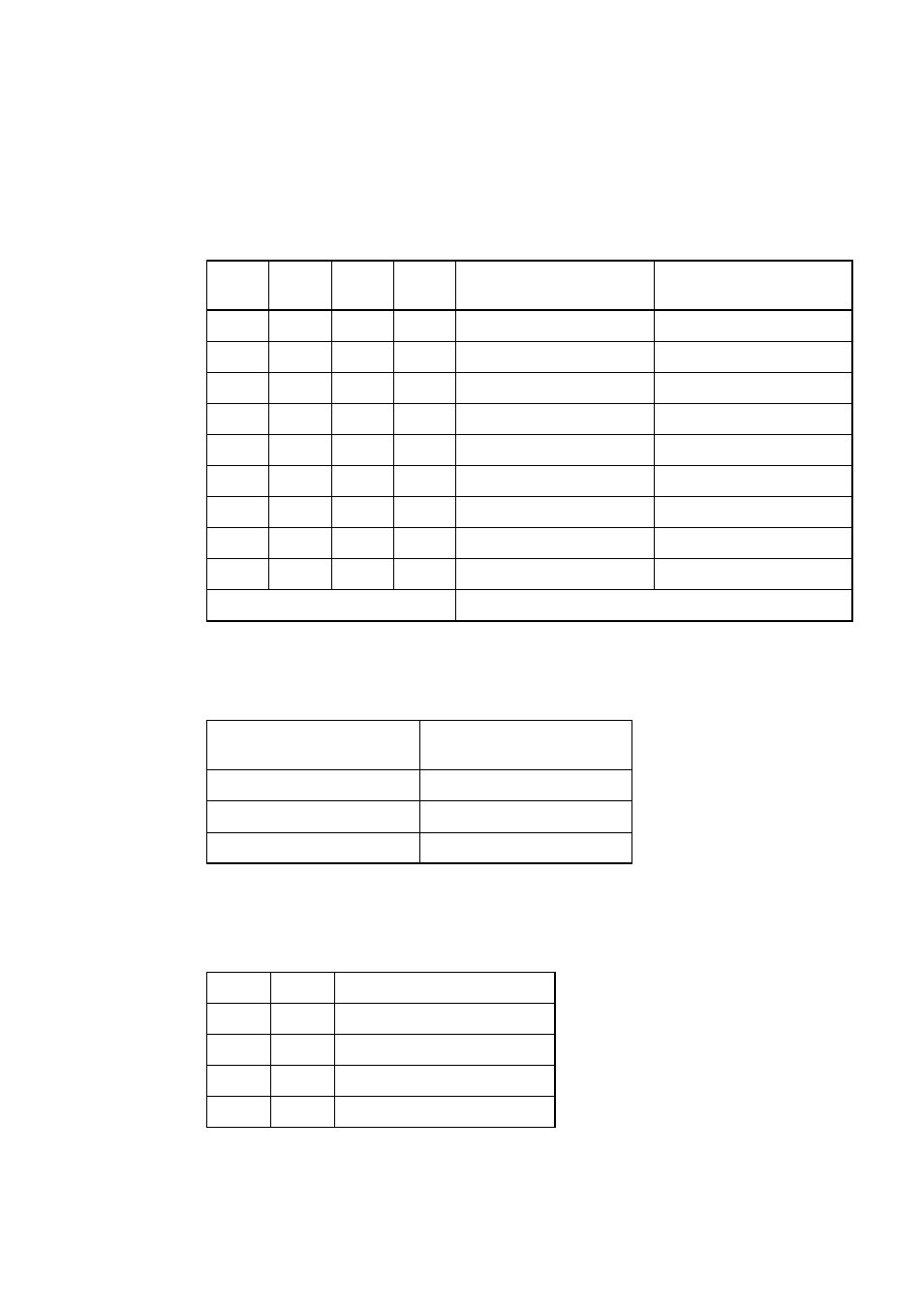

Table 15.5-1 lists the available combinations of these bits.

The unit in which an address is incremented or decremented in address update mode varies

depending on the specified transfer data size as shown below.

[bits 3,2] WS1, WS0

These bits specify the size of data to be transferred.

Table 15.5-1 Specification of Transfer Source or Destination Address Update Modes

SCS1

SCS0

DCS1

DCS0

Transfer source

address

Transfer destination

address

0

0

0

0

Increment

Increment

0

0

0

1

Increment

Decrement

0

0

1

0

Increment

Do not update

0

1

0

0

Decrement

Increment

0

1

0

1

Decrement

Decrement

0

1

1

0

Decrement

Do not update

1

0

0

0

Do not update

Increment

1

0

0

1

Do not update

Decrement

1

0

1

0

Do not update

Do not update

Other

Reserved

Table 15.5-2 Address Increment/Decrement Unit

Transfer data size

Address increment/

decrement unit

byte (8bit)

plus or minus 1 byte

halfword (16bit)

plus or minus 2 byte

word (32bit)

plus or minus 4 byte

Table 15.5-3 Specification of Transfer Data Size

WS1

WS0

Transfer data size

0

0

byte

0

1

halfword

1

0

word

1

1

Reserved