FUJITSU MB91F109 FR30 User Manual

Page 436

412

APPENDIX E Instructions

■

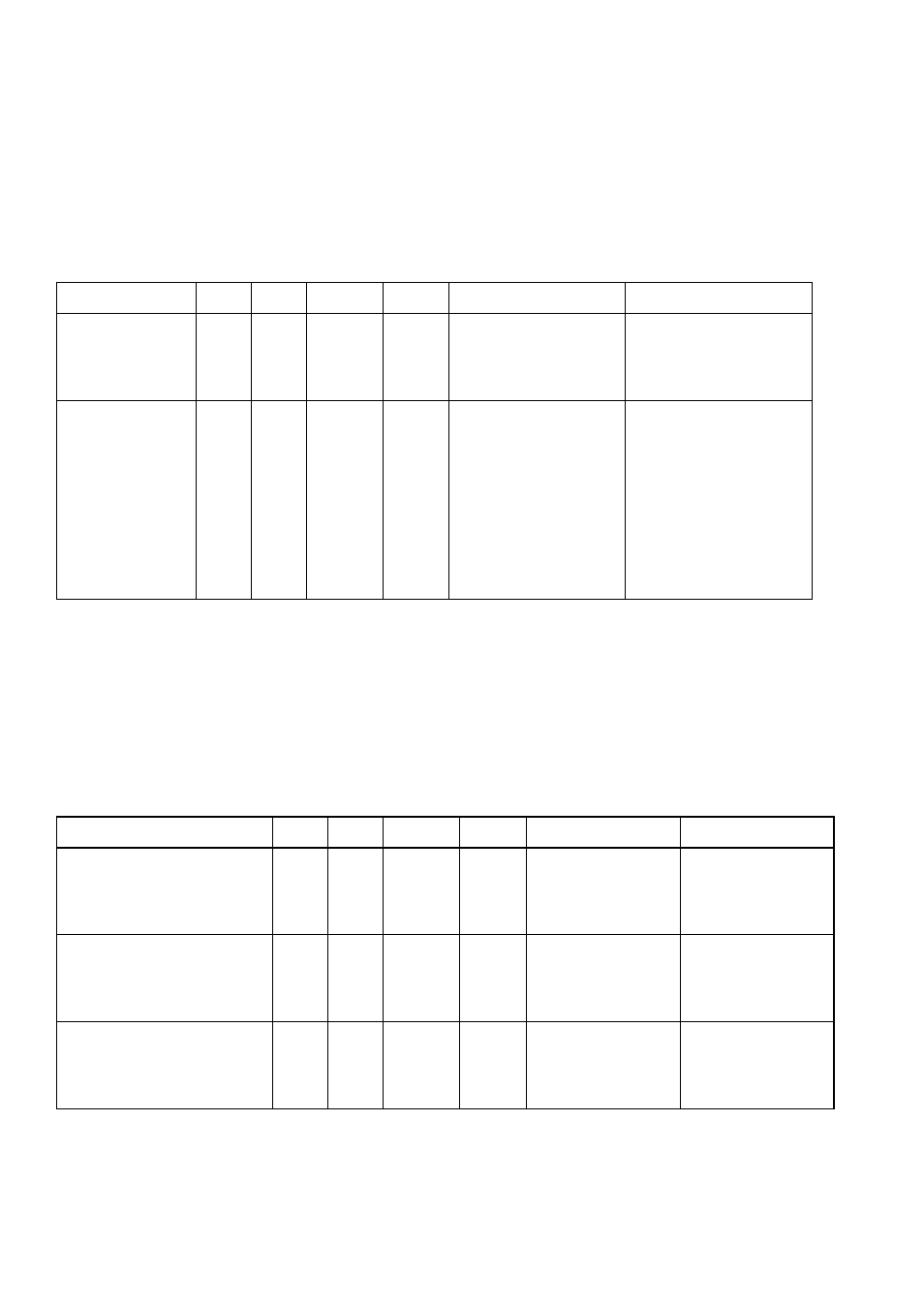

Multiplication and Division Instructions

■

Shift Instructions

*3

The assembler creates BEORL if the bit is ON in u8&0x0F and BEORH if the bit is ON in u8&0xF0.

Both BEORL and BEORH may be created.

Table E.1-5 Multiplication and Division Instructions

Mnemonic

Type

OP

Cycle

NZVC

Operation

Remarks

MUL

Rj,Ri

MULU Rj,Ri

MULH Rj,Ri

MULUH Rj,Ri

A

A

A

A

AF

AB

BF

BB

5

5

3

3

CCC-

CCC-

CC--

CC--

Ri × Rj --> MDH,MDL

Ri × Rj --> MDH,MDL

Ri × Rj --> MDL

Ri × Rj --> MDL

32-bit × 32-bit = 64-bit

Unsigned

16-bit × 16-bit = 32-bit

Unsigned

DIVOS Ri

DIVOU Ri

DIV1

Ri

DIV2

Ri*

3

DIV3

DIV4S

*DIV

Ri*

1

*DIVU Ri*

2

E

E

E

E

E

E

97-4

97-5

97-6

97-7

9F-6

9F-7

1

1

d

1

1

1

36

33

----

----

-C-C

-C-C

----

----

-C-C

-C-C

MDL / Ri --> MDL ,

MDL % Ri --> MDH

MDL / Ri --> MDL ,

MDL % Ri --> MDH

Step operation

32bit/32bit=32bit

*1

DIV0S, DIV1× 32, DIV2, DIV3, and DIV4S are created. The instruction code length becomes 72 bytes.

*2

DIV0U and DIV1× 32 are created. The instruction code length becomes 66 bytes.

*3

Put a DIV3 instruction after the DIV2 instruction.

Table E.1-6 Shift Instructions

Mnemonic

Type

OP

Cycle

NZVC

Operation

Remarks

LSL

Rj, Ri

*LSL

#u5, Ri (u5: 0 to 31)

LSL

#u4, Ri

LSL2

#u4, Ri

A

C'

C

C

B6

B4

B4

B5

1

1

1

1

CC-C

CC-C

CC-C

CC-C

Ri << Rj --> Ri

Ri << u5 --> Ri

Ri << u4 --> Ri

Ri <<(u4+16) --> Ri

Logical shift

LSR

Rj, Ri

*LSR

#u5, Ri (u5: 0 to 31)

LSR

#u4, Ri

LSR2 #u4, Ri

A

C'

C

C

B2

B0

B0

B1

1

1

1

1

CC-C

CC-C

CC-C

CC-C

Ri >> Rj --> Ri

Ri >> u5 --> Ri

Ri >> u4 --> Ri

Ri >>(u4+16) --> Ri

Logical shift

ASR

Rj, Ri

*ASR

#u5, Ri (u5: 0 to 31)

ASR

#u4, Ri

ASR2 #u4, Ri

A

C'

C

C

BA

B8

B8

B9

1

1

1

1

CC-C

CC-C

CC-C

CC-C

Ri >> Rj --> Ri

Ri >> u5 --> Ri

Ri >> u4 --> Ri

Ri >>(u4+16) --> Ri

Logical shift