5 area mode register 0 (amd0) – FUJITSU MB91F109 FR30 User Manual

Page 145

121

4.5 Area Mode Register 0 (AMD0)

4.5

Area Mode Register 0 (AMD0)

Area mode register 0 (AMD0) specifies the operation mode of chip select area 0 (area

other that those specified by ASR1 to ASR5 and AMR1 to AMR5). At reset time, area 0

is selected.

■

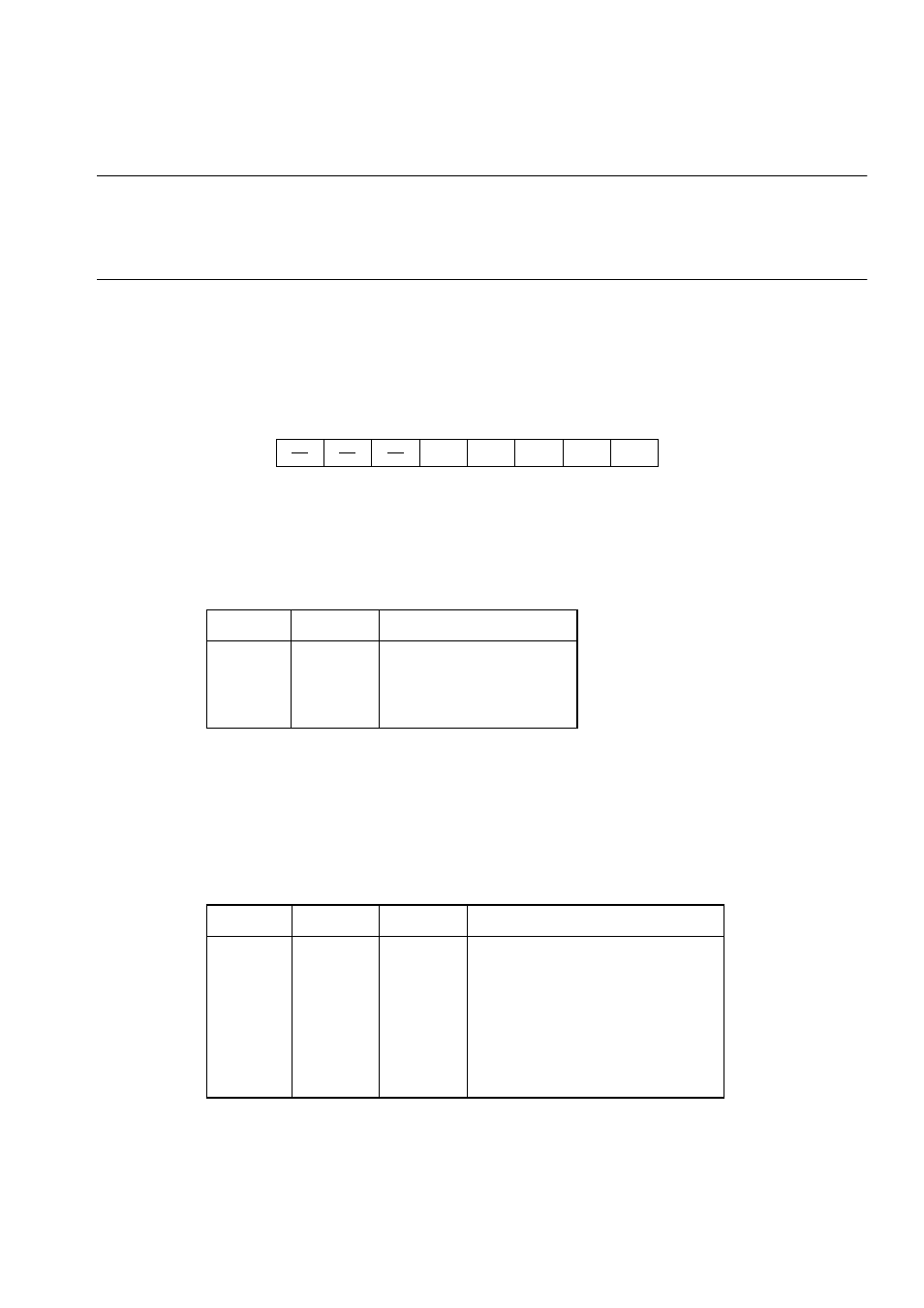

Configuration of Area Mode Register 0 (AMD0)

Area mode register 0 (AMD0) is configured as follows:

■

Bit Functions of Area Mode Register 0 (AMD0)

[bit 4 and 3] BW1 and 0 (Bus Width bit)

BW1 and BW0 specify the bus width of area 0.

The initial values of both BW1 and BW0 are "0"; however, not register values but the MD1 and

MD0 pin level outputs are read at read time until writing to the MODR.

[bit 2 to 0] WTC 2 to 0 (Wait Cycle bit)

WTC2 to WTC0 specify the number of wait cycles to be automatically inserted when the

usual bus interface is running.

WTC2 to WTC0 of AMD0 are reset to "111", so that seven wait cycles are automatically

inserted at bus access time immediately after the reset is released.

7

6

5

4

3

2

1

0

AMD0

Address: 0000 0620

H

BW1

BW0 WTC2 WTC1 WTC0

---00111

H

R/W

Initial value

Access

BW1

BW0

Bus width

0

0

1

1

0

1

0

1

8 bits

16 bits

Setting not possible

Setting not possible

WTC2

WTC1

WTC0

Number of inserted wait cycles

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

2

3

4

5

6

7