FUJITSU MB91F109 FR30 User Manual

Page 434

410

APPENDIX E Instructions

■

Addition and Subtraction Instructions

■

Compare Operation Instructions

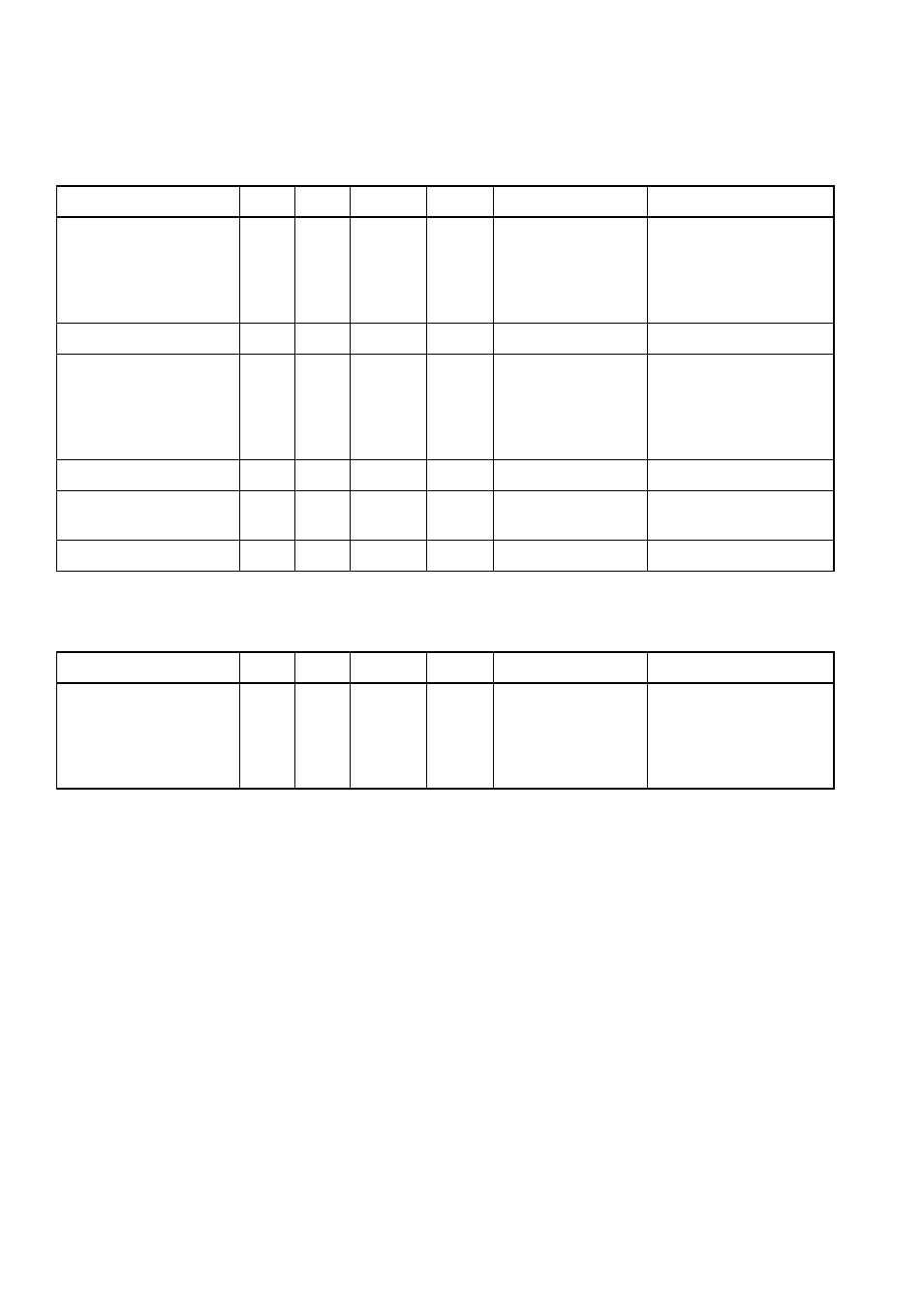

Table E.1-1 Addition and Subtraction Instructions

Mnemonic

Type

OP

Cycle

NZVC

Operation

Remarks

ADD

Rj, Ri

*ADD #s5, Ri

ADD

#i4, Ri

ADD2 #i4, Ri

A

C’

C

C

A6

A4

A4

A5

1

1

1

1

CCCC

CCCC

CCCC

CCCC

Ri + Rj --> Ri

Ri + s5 --> Ri

Ri + extu(i4) --> Ri

Ri + extu(i4) --> Ri

Upper 1 bit is read as a

code by the assembler.

Zero expansion

Negative expansion

ADDC Rj, Ri

A

A7

1

CCCC

Ri + Rj + c --> Ri

Addition with carry-over

ADDN Rj, Ri

*ADDN #s5, Ri

ADDN #i4, Ri

ADDN2#i4, Ri

A

C'

C

C

A2

A0

A0

A1

1

1

1

1

----

----

----

----

Ri + Rj --> Ri

Ri + s5 --> Ri

Ri + extu(i4) --> Ri

Ri + extu(i4) --> Ri

Upper 1 bit is read as a

code by the assembler.

Zero expansion

Negative expansion

SUB

Rj, Ri

A

AC

1

CCCC

Ri - Rj --> Ri

SUBC Rj, Ri

A

AD

1

CCCC

Ri - Rj - c --> Ri

Subtraction with carry-

over

SUBN Rj, Ri

A

AE

1

----

Ri - Rj --> Ri

Table E.1-2 Compare Operation Instructions

Mnemonic

Type

OP

Cycle

NZVC

Operation

Remarks

CMP

Rj, Ri

*CMP #s5, Ri

CMP

#i4, Ri

CMP2 #i4, Ri

A

C'

C

C

AA

A8

A8

A9

1

1

1

1

CCCC

CCCC

CCCC

CCCC

Ri - Rj

Ri - s5

Ri + extu(i4)

Ri + extu(i4)

Upper 1 bit is read as a

code by the assembler.

Zero expansion

Negative expansion