FUJITSU MB91F109 FR30 User Manual

Page 440

416

APPENDIX E Instructions

■

Delayed-Branch Instructions

(Notes)

•

The assembler calculates and sets values in the rel11 and rel8 fields of the hardware

specification as follows:

(label12-PC-2)/2 -> rel11, (label9-PC-2)/2 -> rel8: Label12 and label9 are signed.

•

The next instruction (delay slot) is executed before delayed branch is executed.

•

All 1-cycle instructions including the a, b, c, and d cycle instructions can be placed in the

delay slot. Instructions of two or more cycles cannot be placed.

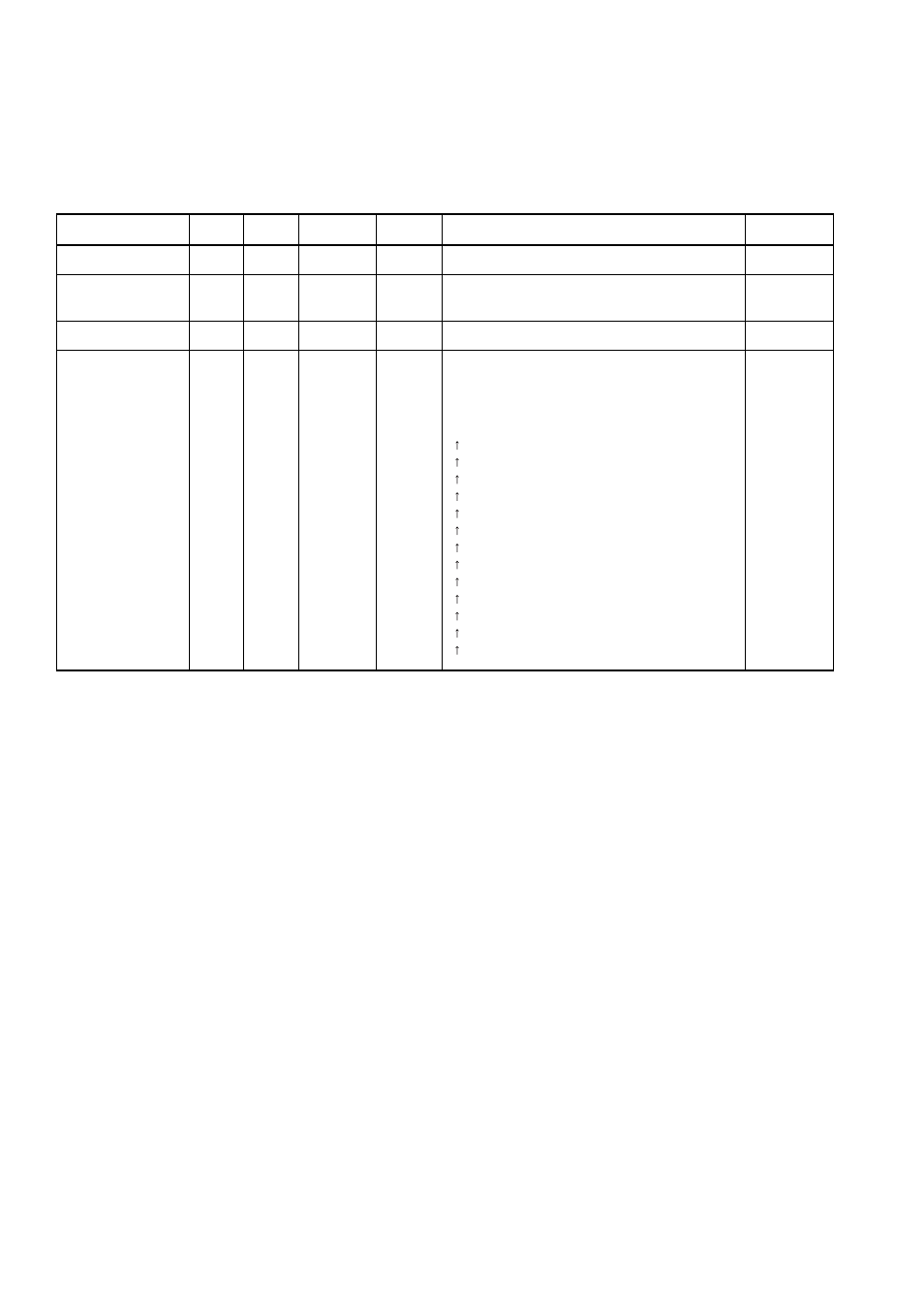

Table E.1-12 Delayed Branch Instructions

Mnemonic

Type

OP

CYCLE

NZVC

Operation

Remarks

JMP:D @Ri

E

9F-0

1

----

Ri --> PC

CALL:D label12

CALL:D @Ri

F

E

D8

9F-1

1

1

----

----

PC+4-->RP ,PC+2+(label12-PC-2) -->PC

PC+4-->RP ,Ri-->PC

RET:D

E

9F-2

1

----

RP --> PC

Return

BRA:D label9

BNO:D label9

BEQ:D label9

D

D

D

F0

F1

F2

1

1

1

----

----

----

PC+2+(label9-PC-2) -->PC

Nonbranch

if(Z==1) then

PC+2+(label9-PC-2) -->PC

BNE:D label9

BC:D

label9

BNC:D label9

BN:D

label9

BP:D

label9

BV:D

label9

BNV:D label9

BLT:D

label9

BGE:D label9

BLE:D label9

BGT:D label9

BLS:D label9

BHI:D label9

D

D

D

D

D

D

D

D

D

D

D

D

D

F3

F4

F5

F6

F7

F8

F9

FA

FB

FC

FD

FE

FF

1

1

1

1

1

1

1

1

1

1

1

1

1

----

----

----

----

----

----

----

----

----

----

----

----

----

s/Z==0

s/C==1

s/C==0

s/N==1

s/N==0

s/V==1

s/V==0

s/V xor N==1

s/V xor N==0

s/(V xor N) or Z==1

s/(V xor N) or Z==0

s/C or Z==1

s/C or Z==0