9 dmac timing charts – FUJITSU MB91F109 FR30 User Manual

Page 366

342

CHAPTER 15 DMAC

15.9 DMAC Timing Charts

This section provides the following DMAC timing charts:

• Timing charts for the descriptor access block

• Timing charts for the data transfer block

• Transfer stop timing charts in continuous transfer mode

• Transfer termination timing charts

■

Codes Used in the Timing Charts

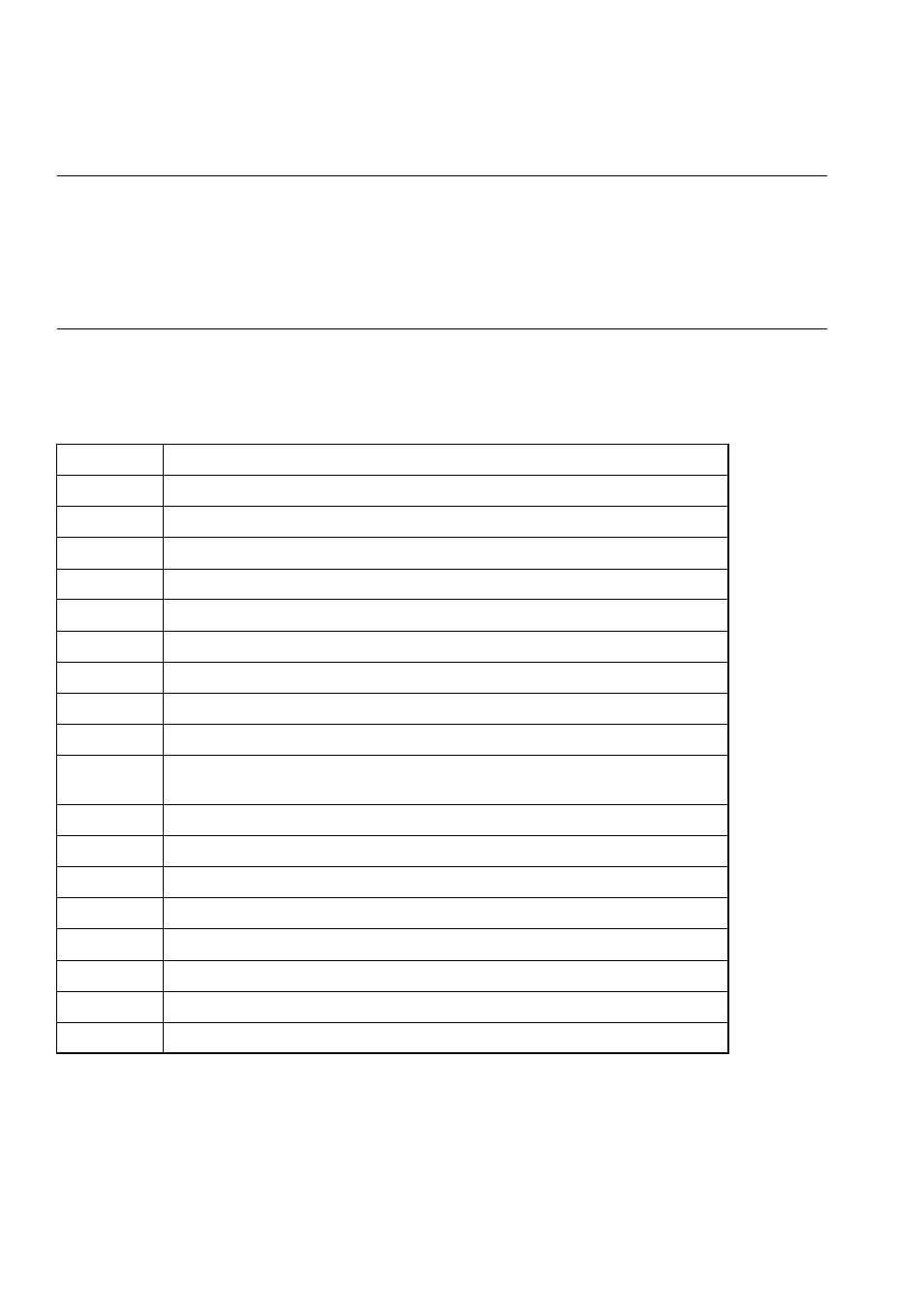

Table 15.9-1 Codes Used in the Timing Charts

Code

Meaning

#0

Descriptor No.0

#0H

Bit 31 to bit 16 of descriptor No. 0

#0L

Bit 15 to bit 0 of descriptor No. 0

#1

Descriptor No. 1

#1H

Bit 31 to bit 16 of descriptor No. 1

#1L

Bit 15 to bit 0 of descriptor No. 1

#2

Descriptor No. 2

#2H

Bit 31 to bit 16 of descriptor No. 2

#2L

Bit 15 to bit 0 of descriptor No. 2

#1/2

Descriptor No. 1 or No. 2 (determined by SCS1 and SCS0 and DCS1 and

DCS0)

#1/2H

Bits 31 to 16 of Descriptor No.1 or 2

#1/2L

Bit 15 to bit 0 of descriptor No. 1 or No. 2

S

Transfer source

SH

Bits 31 to 16 of transfer source

SL

Bits 15 to 0 of transfer source

D

Transfer destination

DH

Bit 31 to bit 16 of the transfer destination

DL

Bit 15 to bit 0 of the transfer source