FUJITSU MB91F109 FR30 User Manual

Page 260

236

CHAPTER 8 INTERRUPT CONTROLLER

8.8

Example of Using the Hold Request Cancel Request

Function (HRCR)

When the CPU is to perform priority processing during DMA transfer, the DMA side

must cancel the hold request and release the CPU from the hold state. An example of

an interrupt occurring for DMA to cancel the hold request and allow CPU priority

operation is as follows.

■

Control Registers

❍

Hold request cancel request level register (HRCL): This module

When an interrupt having a level higher than that set in the HRCL register occurs, a hold

request cancel request is issued to DMA. Set the reference level for this operation.

❍

Interrupt control register (ICR): This module

Set a level higher than that set in the HRCL register in the ICR corresponding to the interrupt

cause used.

❍

Postpone DMA request register (PDRR): Clock controller

The PDRR is used to temporarily suppress a hold request from DMA and prevent the CPU from

returning to the hold state when the interrupt cause is cleared. A hold request from DMA is

transmitted to the CPU only when the value of this register is 0000

B

. Increment the value of this

register at the beginning of the interrupt routine and decrement it at the exit of the routine.

■

Hardware Configuration

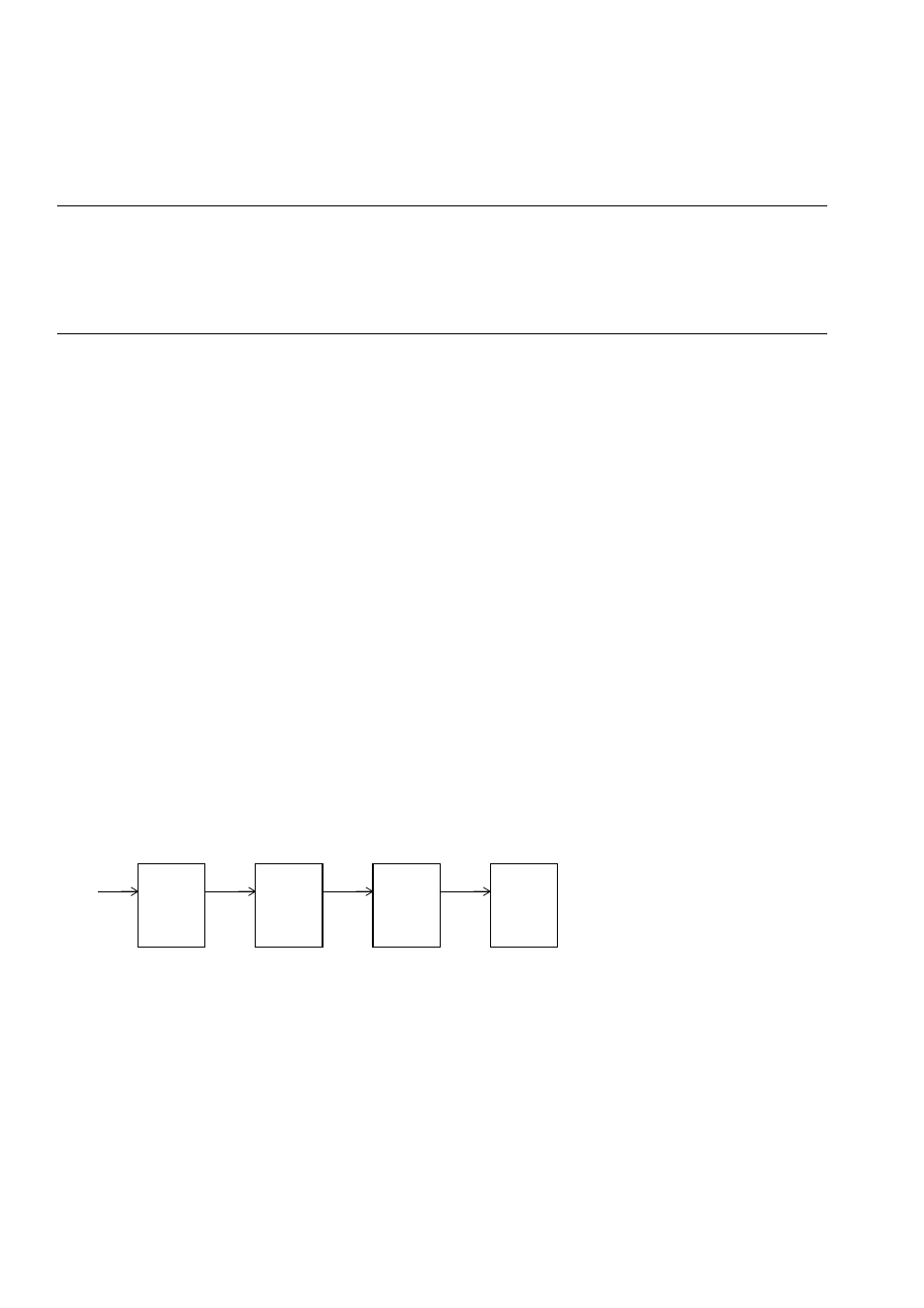

A signal stream is shown below:

Figure 8.8-1 Example of Hardware Configuration for Using the Hold Request Cancel Request Function

IRQ

(ICR)

DMA

CPU

(HRCL)

HRCR

DHRQ (PDRR)

HRQ

This module

Clock controller

DHRQ: DMA hold request

HRQ: Hold request

IRQ: Interrupt request

HRCR: Hold request cancel request