How to read this manual – FUJITSU MB91F109 FR30 User Manual

Page 9

v

How to Read This Manual

■

Description Format of this Manual

Major terms used in this manual are explained below:

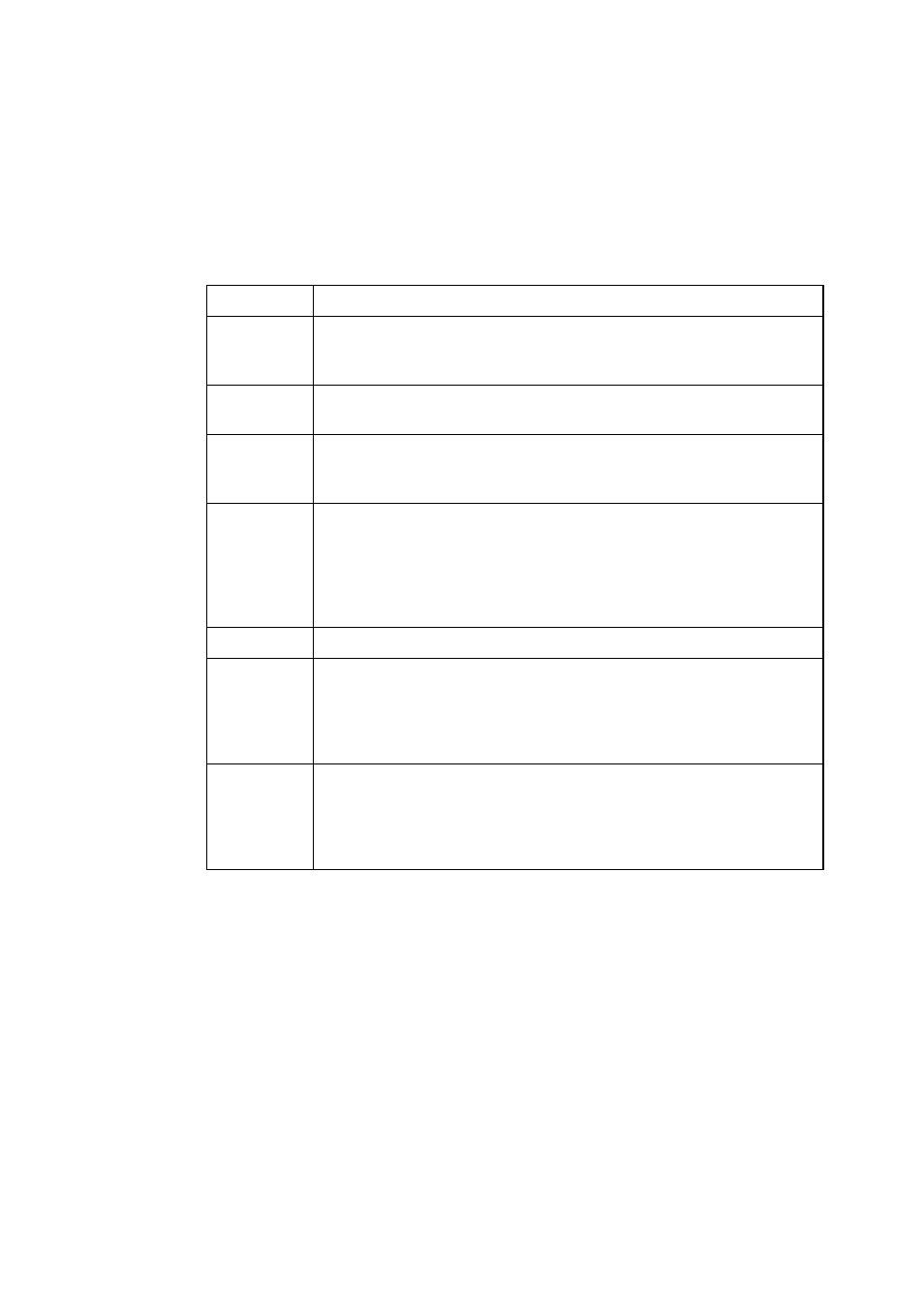

Term

Meaning

I-BUS

16-bit wide bus used for internal instructions. Since the FR series uses

an internal Harvard architecture, independent buses are used for

instructions and data. A bus converter is connected to the I-BUS.

D-BUS

Internal 32-bit wide data bus. Internal resources are connected to the

D-BUS.

C-BUS

Internal multiplex bus. The C-BUS is connected to the I-BUS and D-

BUS via a switch. An external interface module is connected to the C-

BUS. Data and instructions are multiplexed in the external data bus.

R-BUS

Internal 16-bit wide data bus. The R-BUS is connected to the D-BUS

via an adapter. Various I/O ports, the clock generator, and interrupt

controller are connected to the R-BUS. Since the R-BUS is 16 bits

wide in which addresses and data are multiplexed, it takes twice as

much or more cycle time than usual for the CPU to access these

resources.

E-unit

Operation executing unit

φ

System clock output from the clock generator to each internal resource

connected to the R-BUS. The system clock at the highest speed

shows the same cycle as source oscillation but is divided into 1, 1/2, 1/

4, and 1/8 (or 1/2, 1/4, 1/8, and 1/16) by PCK1 and PCK0 of the clock

generator GCR register.

θ

System clock or operation clock for the CPU and resources connected

to a bus other than the R-BUS. The system clock at the highest speed

shows the same cycle as source oscillation but is divided into 1, 1/2, 1/

4, and 1/8 (or 1/2, 1/4, 1/8, and 1/16) by CCK1 and CCK0 of the clock

generator GCR register.