FUJITSU MB91F109 FR30 User Manual

Page 285

261

10.9 UART Interrupt Occurrence and Flag Setting Timing

■

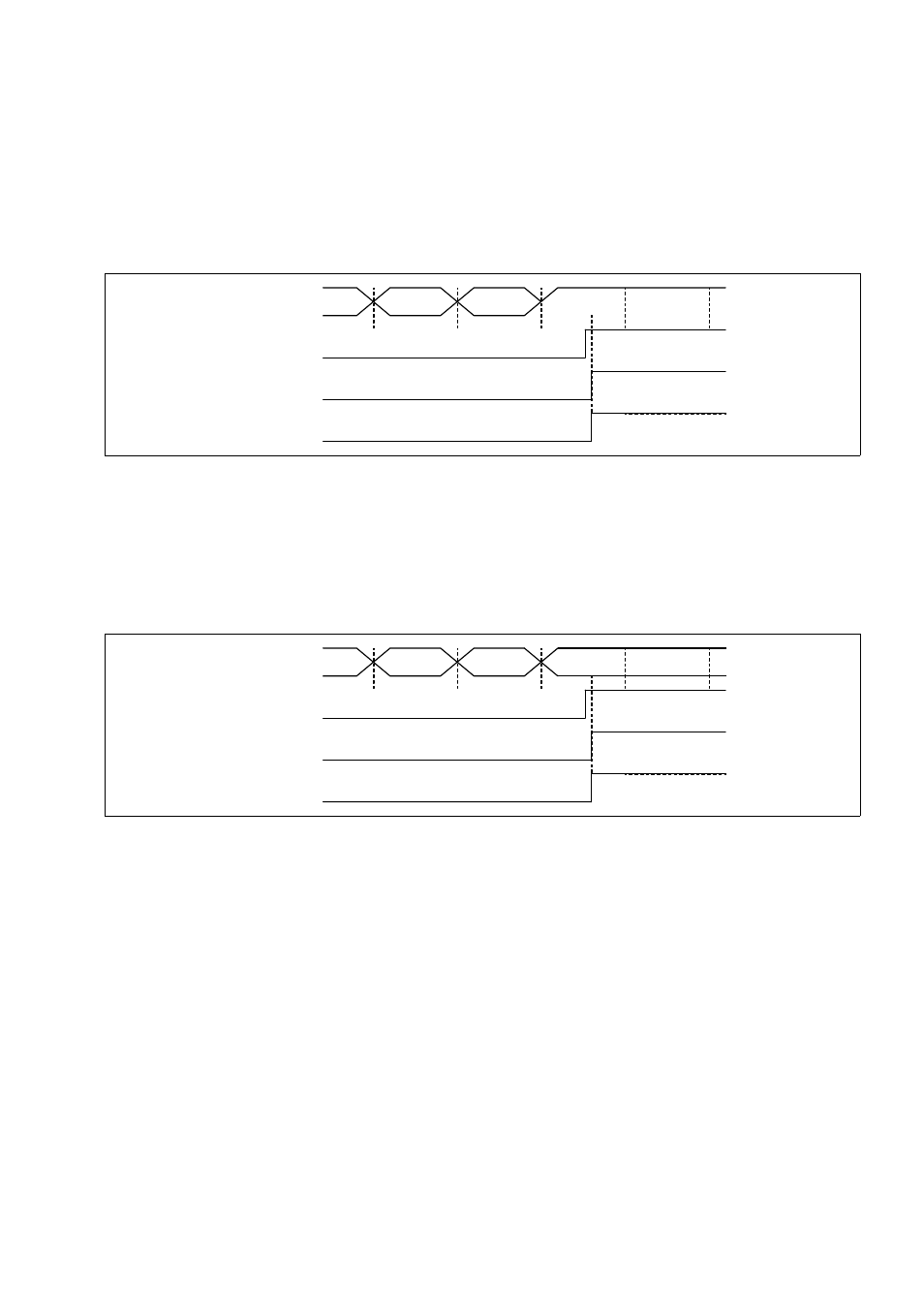

Interrupt Flag Set Timing for Data Recepion in Mode 1

When the last stop bit is detected after data reception/transfer is completed, the ORE, FRE, and

RDRF flags are set to issue an interrupt request to the CPU. Since the length of data items that

can be received is eight bits, the data at the last bit, bit 9, indicates an address or that data is

invalid. If ORE or FRE is active, the SIDR data is invalid.

Figure 10.9-2 ORE, FRE, and RDRF Set Timing (Mode 1)

■

Interrupt Flag Set Timing for Data Reception in Mode 2

When the last data item (D7) is detected after data reception/transfer is completed, the ORE

and RDRF flags are set to issue an interrupt request to the CPU. If ORE is active, the SIDR

data is invalid.

Figure 10.9-3 ORE and RDRF Set Timing (Mode 2)

D7

Stop

ORE, FRE

RDRF

Reception interrupt

Data

Address/

data

D5

D6

D7

ORE

RDRF

Reception interrupt

Data

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (102 pages)

- T5140 (76 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MPE3XXXAT (191 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)