5 priority check – FUJITSU MB91F109 FR30 User Manual

Page 255

231

8.5 Priority Check

8.5

Priority Check

IWhen multiple interrupt causes are generated simultaneously, this module selects one

having the highest priority and posts the interrupt level and number of the cause to the

CPU.

NMI is given the highest priority among the interrupt causes handled by this module.

■

Priority Check

The criteria for checking the priority of interrupt causes are as follows:

1. NMI

2. Cause that satisfies the following conditions:

•

Causes in an interrupt level other than 31 (interrupt inhibited for level 31)

•

Causes in the lowest interrupt level

•

Among these causes, one with the smallest interrupt number

Table 8.5-1 summarizes the relationships among interrupt causes, numbers, and levels.

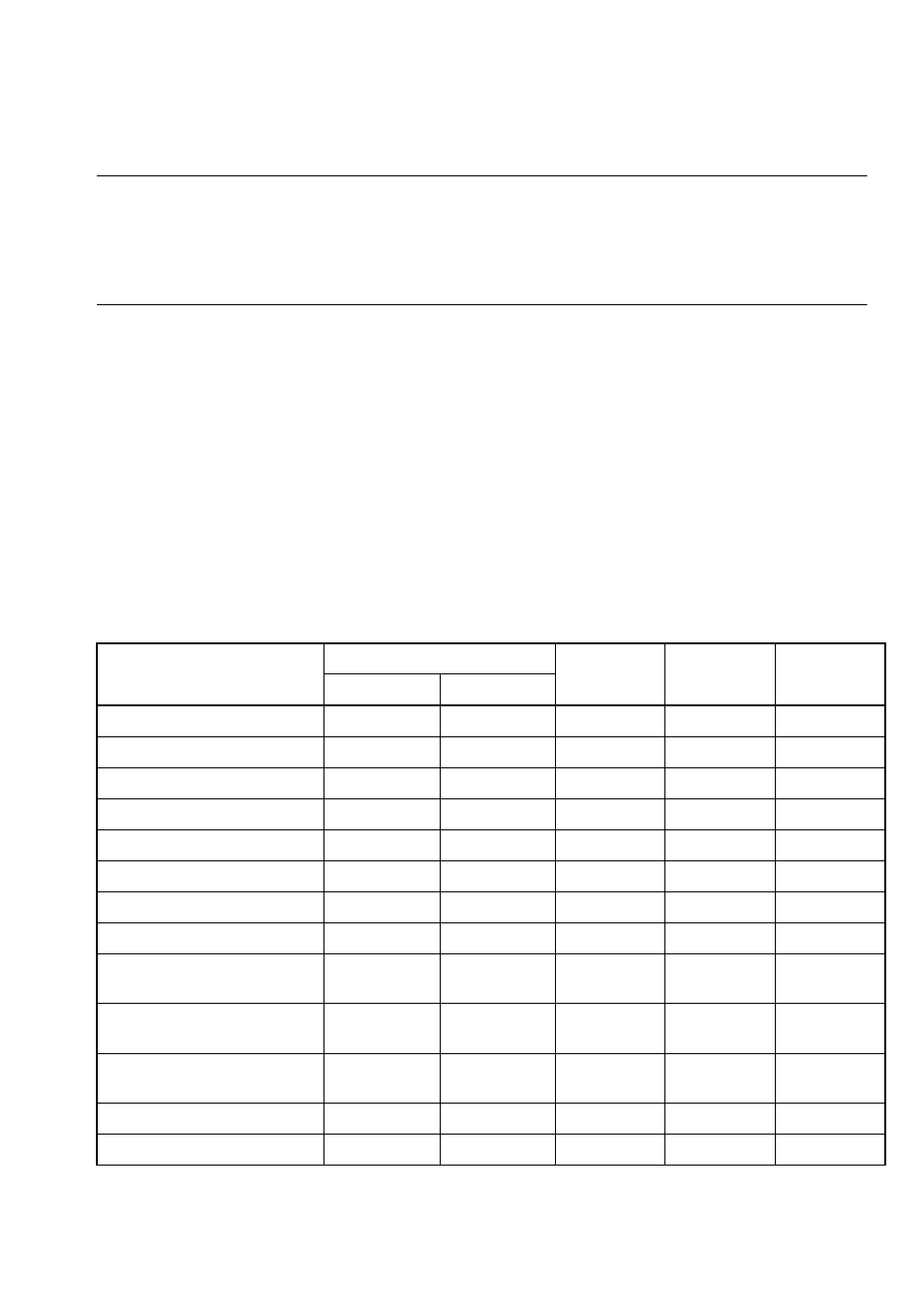

Table 8.5-1 Relationships among Interrupt Causes, Numbers, and Levels (1/2)

Cause of interrupt

Interrupt number

Interrupt

level

Offset

TBR default

address

Decimal

Hexadecimal

NMI request

15

0F

15(F

H

) fixed

3C0

H

000FFFC0

H

External interrupt 0

16

10

ICR00

3BC

H

000FFFBC

H

External interrupt 1

17

11

ICR01

3B8

H

000FFFB8

H

External interrupt 2

18

12

ICR02

3B4

H

000FFFB4

H

External interrupt 3

19

13

ICR03

3B0

H

000FFFB0

H

UART 0 reception complete

20

14

ICR04

3AC

H

000FFFAC

H

UART 1 reception complete

21

15

ICR05

3A8

H

000FFFA8

H

UART 2 reception complete

22

16

ICR06

3A4

H

000FFFA4

H

UART 0 transmission

complete

23

17

ICR07

3A0

H

000FFFA0

H

UART 1 transmission

complete

24

18

ICR08

39C

H

000FFF9C

H

UART 2 transmission

complete

25

19

ICR09

398

H

000FFF98

H

DMAC 0 (end, error)

26

1A

ICR10

394

H

000FFF94

H

DMAC 1 (end, error)

27

1B

ICR11

390

H

000FFF90

H