17 hyper dram interface: read – FUJITSU MB91F109 FR30 User Manual

Page 212

188

CHAPTER 4 BUS INTERFACE

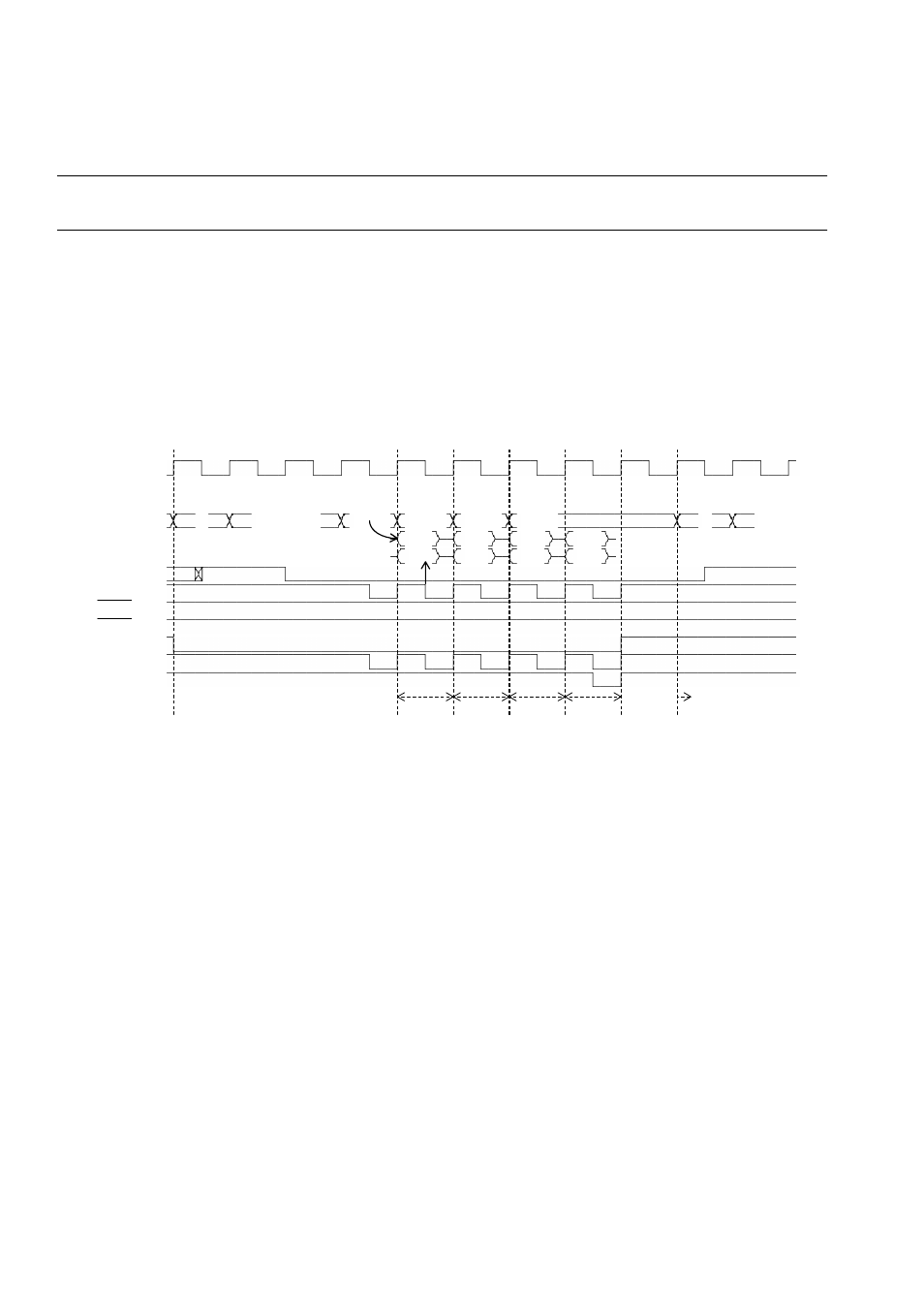

4.17.17 Hyper DRAM Interface: Read

This section provides a hyper DRAM interface timing chart.

■

Hyper DRAM Interface: Read Timing Chart

❍

Bus width: 16 bits, access: words

Figure 4.17-32 Example of Hyper DRAM Interface Read Timing Chart

[Explanation of operation]

•

Column addresses are output in Q4HR cycles.

•

CAS is asserted at the falling edge of Q4HR and negated at the rising edge of Q4HR.

•

D31 to D16 are fetched at the falling edge of CAS to be output in the Q4HR cycle next to that

in which the corresponding column address is output.

•

After a read cycle ends, at least one idle clock cycle is inserted so as to prevent conflicts

between the external data buses.

•

DACK0 to DACK2 and E0P0 to E0P2 are output at the same time as CAS.

Q1

Q2

Q3

Q4HR

Q4HR

Q4HR

Q4HR

Q4HR

Q1

Q3

CLK

1CAS/2WE

A24-00

X

row.adr.

col.0

col.2

col.4

col.6

X

row.a

D31-24

D23-16

RAS

CAS

WEL

WEH

RDX

(DACK0)

(EOP0)

Outside page

1)

Read1

Read0

Idle

Read3

Read2

Read5

Read4

Read7

Read6

High

speed

page

High

speed

page

High

speed

page

High

speed

page

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (102 pages)

- T5140 (76 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MPE3XXXAT (191 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)