FUJITSU MB91F109 FR30 User Manual

Page 131

107

3.14 Clock Doubler Function

register. (Table 3.14.1 shows an example for the case that a 12.5 MHz oscillation is used.)

*1: Fixed to 1/1 regardless of settings

*2: To disable the clock doubler function, switch the clock to the divide-by-two clock in advance.

*3: When the PLL oscillation frequency is changed, the clock must be switched to the divide-by-

two clock.

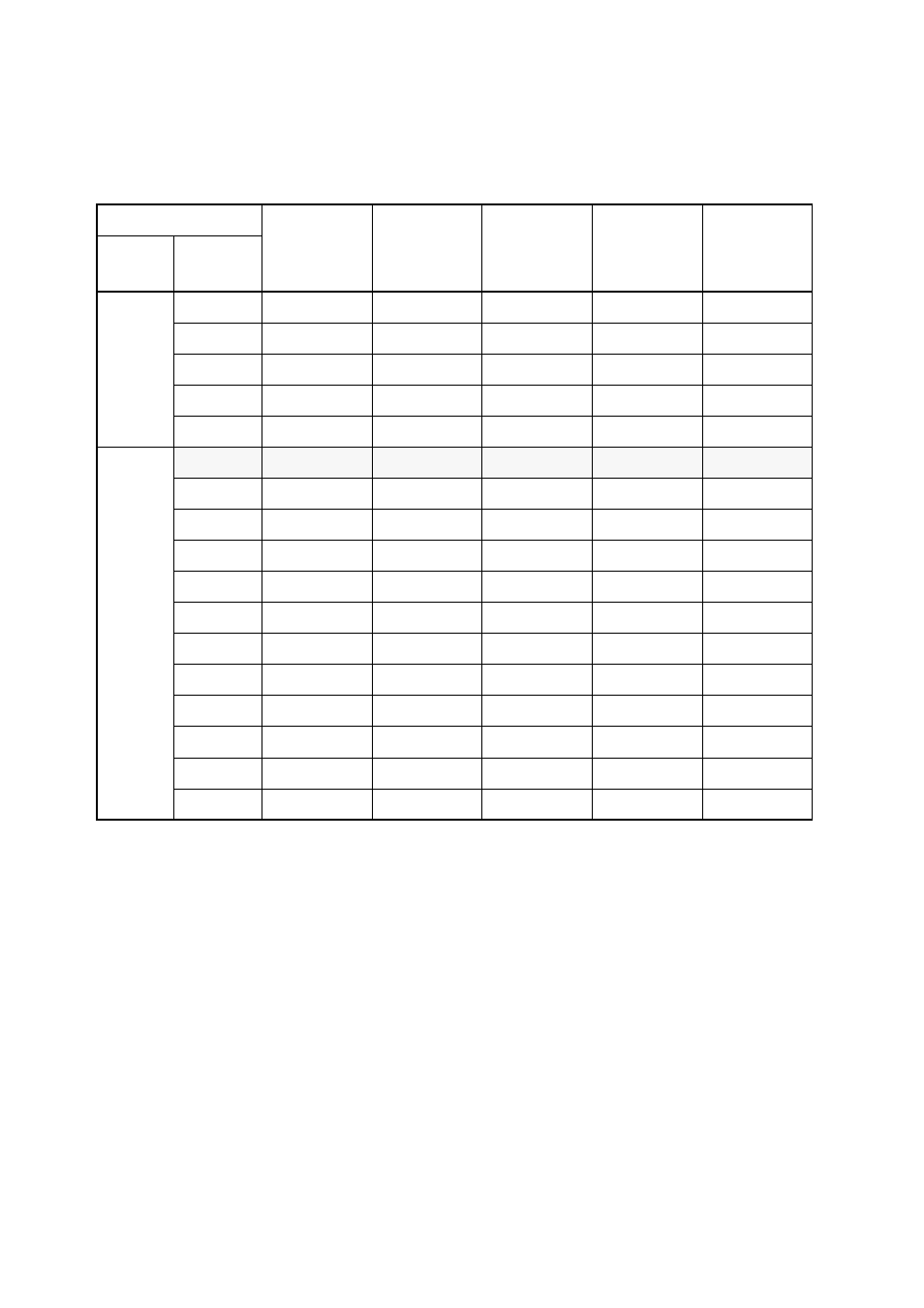

Table 3.14-1 Operating Frequency Combinations Depending on whether the Clock Doubler Function is

Enabled or Disabled

GCR

PLL

oscillation

frequency

(MHz)

Clock

doubler

Internal

operating

frequency

(MHz)

External

bus

frequency

(MHz)

Remarks

CHC

Gear

Divide-

by-two

1/1

OFF

6.25

6.25

1/2

OFF

3.12

3.12

1/4

OFF

1.56

1.56

1/8

OFF

0.78

0.78

Initial value

(*1)

ON

6.25

3.12

PLL *

3

-

50.0

OFF

50.0

50.0

Inhibited

1/1

25.0

OFF

25.0

25.0

1/2

25.0

OFF

12.5

12.5

1/4

25.0

OFF

6.25

6.25

1/8

25.0

OFF

3.12

3.12

1/1

12.5

OFF

12.5

12.5

1/2

12.5

OFF

6.25

6.25

1/4

12.5

OFF

3.12

3.12

1/8

12.5

OFF

1.56

1.56

*1

50.0

ON

50.0

25.0

*2

*1

25.0

ON

25.0

12.5

*1

12.5

ON

12.5

6.25

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (102 pages)

- T5140 (76 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MPE3XXXAT (191 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)