1 stop state – FUJITSU MB91F109 FR30 User Manual

Page 116

92

CHAPTER 3 CLOCK GENERATOR AND CONTROLLER

3.10.1 Stop State

This section provides information on transition to and returning from the stop state.

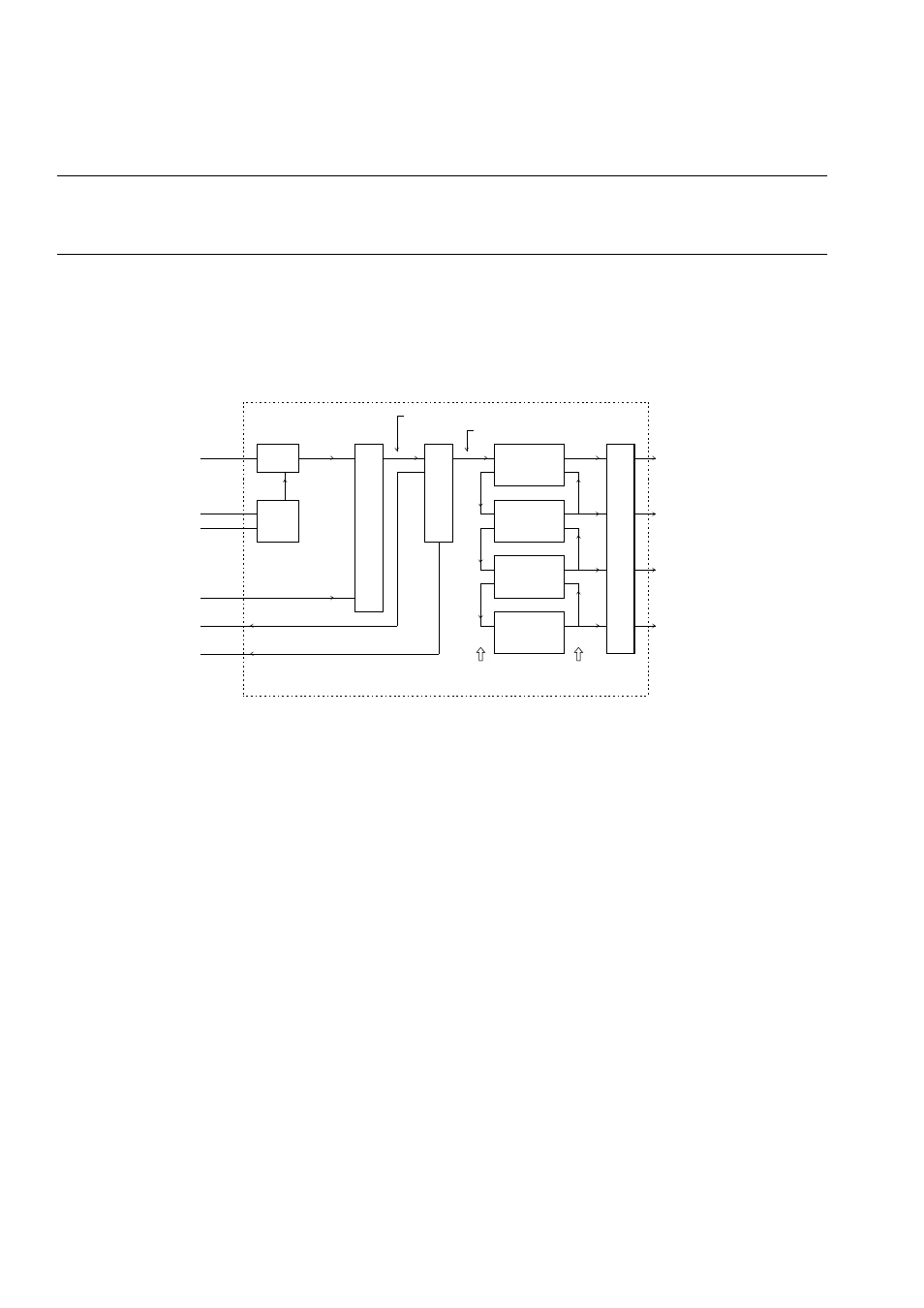

Figure 3.10.1 shows a stop controller block diagram.

■

Stop Controller Block Diagram

Figure 3.10-1 Stop Controller Block Diagram

■

Transition to Stop State

❍

Transition to the stop state using an instruction

Write "1" to bit 7 of the STCR register to cause a transition to the stop state.

A stop request is issued, and when the CPU no longer uses the internal bus, the clocks are

stopped in the following order:

CPU clock --> internal bus clock --> internal DMA clock --> internal peripheral clock

The oscillation circuit stops when the internal peripheral clock stops.

•

Proceed as follows to cause a transition to the stop state using an instruction.

•

Before writing to the STCR, set the same value in CCK1/CCK0 and PCK1/PCK0 of the GCR

to match the CPU clock and peripheral clock gear ratios.

•

Do not cause a transition to the stop state while the GCR CHC bit is "0" (operating with PLL).

Before causing a transition to the stop state, always set the GCR CHC bit to "1" (divide-by-

two frequency system) to change the clock.

•

At least six consecutive NOP instructions must be provided immediately after writing to the

STCR.

STCR

STOP

clear

.or.

Internal bus

Internal interrupt

Internal reset

CPU hold enabled

CPU hold request

Stop state

indication signal

State tr

ansition control circuit

Stop state transition request signal

Stop signal

State decoder

CPU clock

generation

Internal

bus clock

generation

Internal

DMA clock

generation

Internal

peripheral

clock

generation

Clock stop

request signal

Clock release

request signal

Inter

nal cloc

k gener

ation circuit

CPU clock

Internal bus clock

Internal DMA clock

External bus clock

Internal peripheral clock