Appendix e instructions – FUJITSU MB91F109 FR30 User Manual

Page 427

403

APPENDIX E Instructions

APPENDIX E Instructions

This section lists the instructions for the FR-series. Before the instructions are listed,

the following items are explained:

• How to read instructions

• Addressing mode codes

• Instruction formats

■

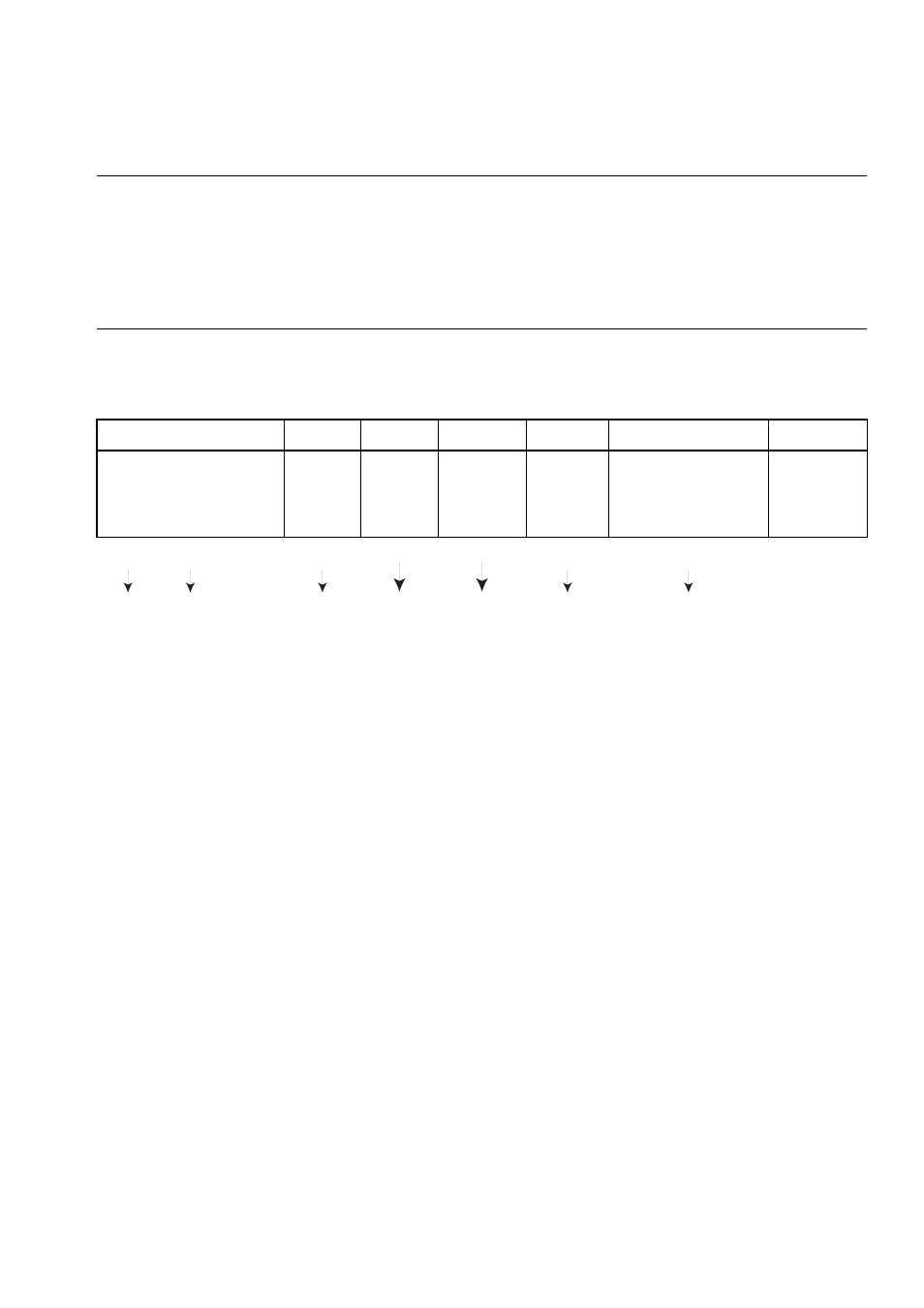

How to Read Instructions

Mnemonic

Type

OP

CYCLE

NZVC

Operation

Remarks

ADD

*ADD

Rj,

#s5,

,

,

Rj

Rj

A

C

,

,

AG

A4

,

,

1

1

,

,

CCCC

CCCC

,

,

Ri + Rj --> Rj

Ri + s5 --> Ri

,

,

(1)

(2)

(3)

(4)

(5)

(6)

(7)

1)

Indicates the instruction names

-

An asterisk (*) indicates extended or assembler instructions that were added to the

standard CPU specifications.

2)

Codes indicating the addressing modes that can be specified in operands

-

For an explanation of codes, see "Addressing mode codes."

3)

Indicates instruction formats

4)

Operation codes are indicated by hexadecimal numbers

5)

Indicates the number of machine cycles

- a:

Indicates memory access cycles that may be extended by the Ready function.

- b:

Indicates memory access cycles that may be extended by the Ready function.

When the next instruction references a register subject to the LD operation, interlock

occurs, increasing the number of execution cycles by 1.

- c:

When the next instruction is a Read or Write instruction for the R15, SSP, or USP, or

is an instruction of format A, interlock occurs and the number of execution cycles

increases by 1 to 2.

- d:

When the next instruction references the MDH/MDL, interlock occurs and the number

of execution cycles increases to 2.

-

The codes a, b, c, and d indicate a minimum of 1 cycle.