FUJITSU MB91F109 FR30 User Manual

Page 437

413

APPENDIX E Instructions

■

Immediate Value Setting or 16/32-Bit Immediate Value Transfer Instruction

■

Memory Load Instructions

*: Special register Rs: TBR, RP, USP, SSP, MDH, MDL

(Notes)

The assembler calculates and sets values in the o8 and o4 fields of hardware specifications as

follows:

Disp10/4 --> o8, disp9/2 --> o8, disp8 --> o8: Disp10, disp9, and disp8 are signed.

Udisp6/4 --> o4: Udisp6 is unsigned.

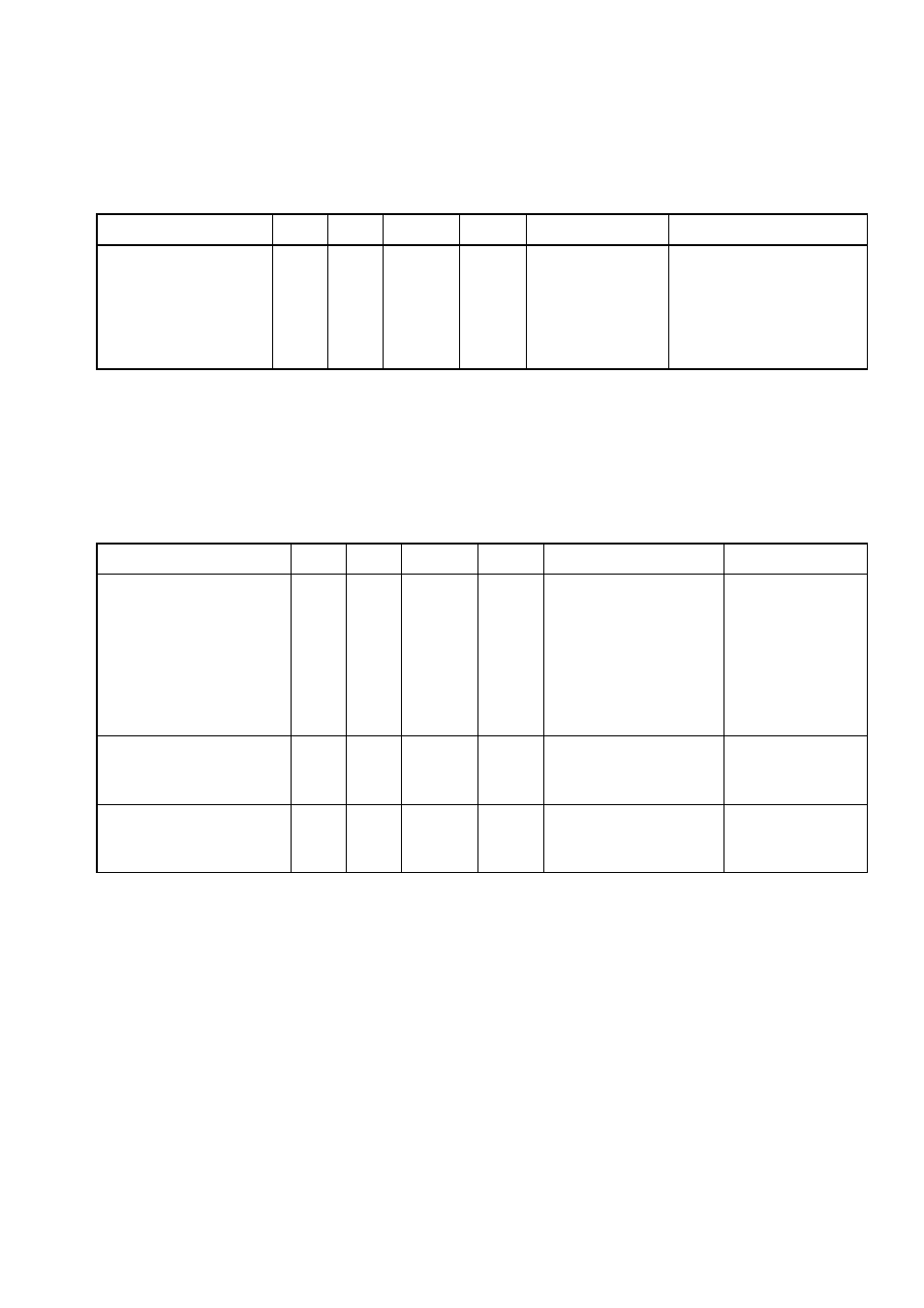

Table E.1-7 Immediate Value Setting or 16/32-Bit Immediate Value Transfer Instruction

Mnemonic

Type

OP

Cycle

NZVC

Operation

Remarks

LDI:32 #i32, Ri

LDI:20 #i20, Ri

LDI:8

#i8, Ri

*LDI #{i8|i20|i32},Ri*

E

C

B

9F-8

9B

C0

3

2

1

----

----

----

i32 --> Ri

i20 --> Ri

i8 --> Ri

{i8|i20|i32} --> Ri

Upper 12 bits are zero-

expanded.

Upper 24 bits are zero-

expanded.

*:

When the immediate value is an absolute value, the assembler automatically selects i8, i20, or i32.

If the immediate value includes a relative value or external reference symbol, i32 is selected.

Table E.1-8 Memory Load Instructions

Mnemonic

Type

OP

CYCLE

NZVC

Operation

Remarks

LD @Rj, Ri

LD @(R13,Rj), Ri

LD @(R14,disp10), Ri

LD @(R15,udisp6), Ri

LD @R15+, Ri

LD @R15+, Rs

LD @R15+, PS

A

A

B

C

E

E

E

04

00

20

03

07-0

07-8

07-9

b

b

b

b

b

b

1+a+b

----

----

----

----

----

----

CCCC

(Rj) --> Ri

(R13 + Rj) --> Ri

(R14 + disp10) --> Ri

(R15 + udisp6) --> Ri

(R15) --> Ri,R15 + = 4

(R15) --> Rs,R15 + = 4

(R15) --> PS,R15 + = 4

Rs: special

register*

LDUH @Rj, Ri

LDUH @(R13,Rj), Ri

LDUH @(R14,disp9), Ri

A

A

B

05

01

40

b

b

b

----

----

----

(Rj) --> Ri

(R13 + Rj) --> Ri

(R14 + disp9) --> Ri

Zero expansion

Zero expansion

Zero expansion

LDUB @Rj, Ri

LDUB @(R13,Rj), Ri

LDUB @(R14,disp8), Ri

A

A

B

06

02

60

b

b

b

----

----

----

(Rj) --> Ri

(R13 + Rj) --> Ri

(R14 + disp8) --> Ri

Zero expansion

Zero expansion

Zero expansion