Table 4–14 – Altera RapidIO MegaCore Function User Manual

Page 97

Chapter 4: Functional Description

4–51

Logical Layer Modules

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

lists the allowed burst count and byteenable combinations for RapidIO IP

core variations with a 64-bit Avalon-MM interface. Avalon-MM value combinations

not listed in

flag interrupts in the RapidIO IP core. For more information

about the relevant interrupts, refer to

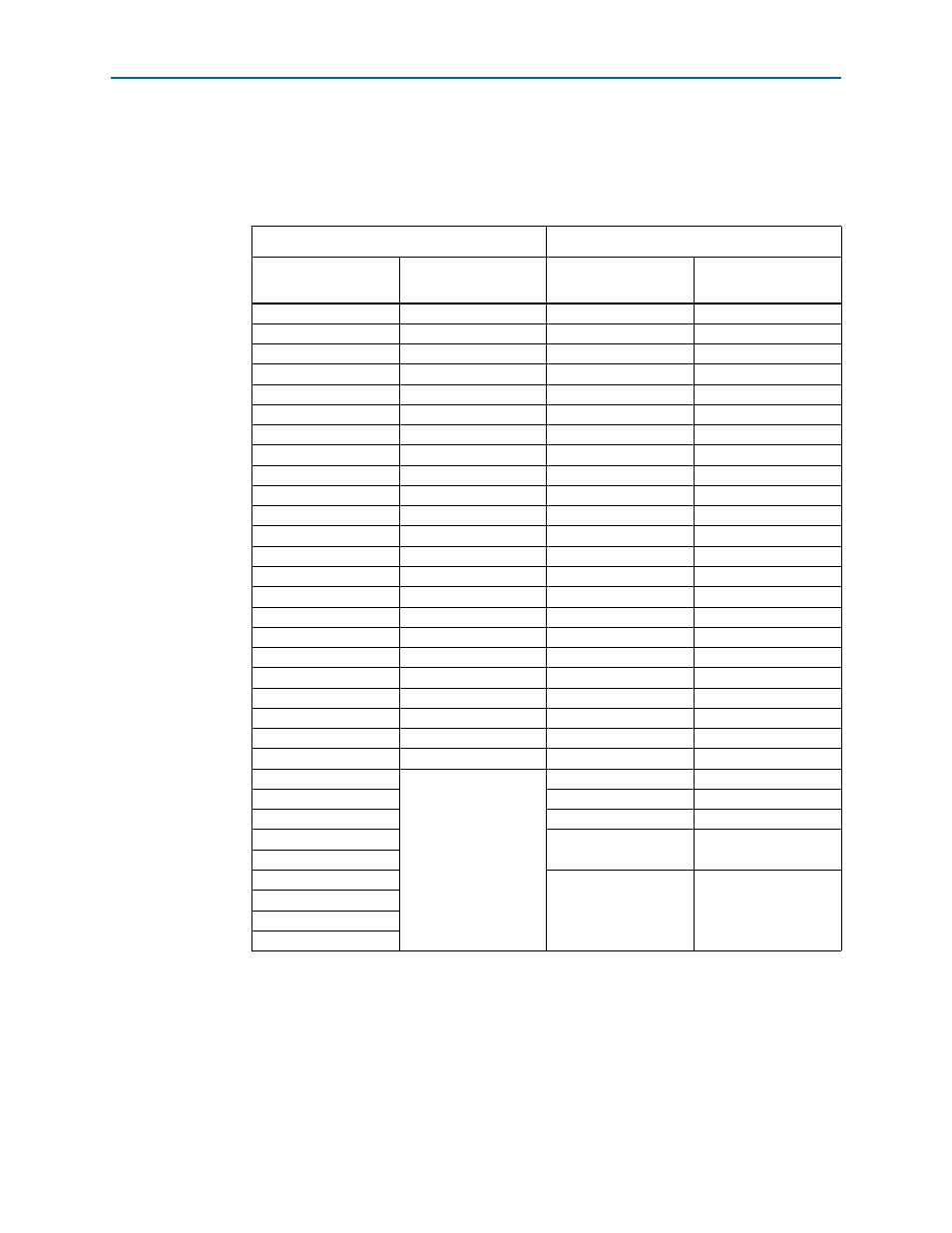

Table 4–14. Write Request Size Encoding (64-bit datapath)

Avalon-MM Values

RapidIO Values

burstcount

byteenable

(8'bxxxx_xxxx)

wdptr

(1'bx)

wrsize

(4'bx)

1

1000_0000

0

0000

1

0100_0000

0

0001

1

0010_0000

0

0010

1

0001_0000

0

0011

1

0000_1000

1

0000

1

0000_0100

1

0001

1

0000_0010

1

0010

1

0000_0001

1

0011

1

1100_0000

0

0101

1

1110_0000

0

0110

1

0011_0000

0

0111

1

1111_1000

0

1000

1

0000_1100

1

1000

1

0000_0111

1

1001

1

0000_0011

1

1001

1

0001_1111

1

1010

1

1111_0000

0

1000

1

0000_1111

1

1000

1

1111_1100

0

1001

1

0011_1111

1

1001

1

1111_1110

0

1010

1

0111_1111

1

1010

1

1111_1111

0

1011

2

1111_1111

1

1011

3–4

0

1100

5–8

1

1100

9–12

1

1101

13–16

17–20

1

1111

21–24

25–28

29–32

Notes to

(1) This is not a legal Avalon-MM byteenable pattern, but the RapidIO IP core supports it if user logic generates it.

(2) For all Avalon-MM write transfers with burstcount larger than 1, io_s_wr_byteenable must be set to

8’b1111_1111

. If it is not, the transfer fails: the INVALID_WRITE_BYTEENABLE bit in the Input/Output Slave

Interrupt

register is set and io_s_mnt_irq is asserted if enabled.