Reset, initialization, and configuration, Reset, initialization, and configuration –3 – Altera RapidIO MegaCore Function User Manual

Page 165

Chapter 7: Testbenches

7–3

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

■

■

In non-Arria 10 variations, the file

performs the test transactions.

In Arria 10 variations, the BFMs, the connections, and the test transaction generation

are integrated in the main testbench file <design_name>_altera_rapidio_140.tb_rio.

The code that performs the test transactions performs a reset and initialization

sequence necessary for the DUT and sister_rio IP cores to establish a link and

exchange packets.

Reset, Initialization, and Configuration

In the testbench generated for non-Arria 10 variations, the clocks that drive the

testbench are defined and generated in the

testbench generated for Arria 10 variations, the clocks are defined and generated in

the main testbench file.

1

Refer to

IP core variation, for the exact frequencies used for each of the clocks. The frequencies

depend on the configuration of the variation.

The reset sequence is simple—the main reset signal for the DUT and the sister_rio IP

core, reset_n, is driven low at the beginning of the simulation, is kept low for 200 ns,

and is then deasserted.

After reset_n is deasserted, the testbench waits until both the DUT and the sister_rio

modules have driven their port_initialized

output signals high. These signal

transitions indicate that both IP cores have completed their initialization sequence.

The testbench then waits an additional 5000 ns, to allow time for a potential reset

link-request control symbol exchange between the DUT and the sister_rio module.

The testbench again waits until both the DUT and the sister_rio modules have driven

their port_initialized output signals high. Following the 5000 ns wait, these signals

indicate that the link is established and the Physical layer is ready to exchange traffic.

Next, basic programming of the internal registers is performed in the DUT and the

sister_rio module.

shows the registers that are programmed in both the

DUT and the sister_rio IP cores. For a full description of each register, refer to

.

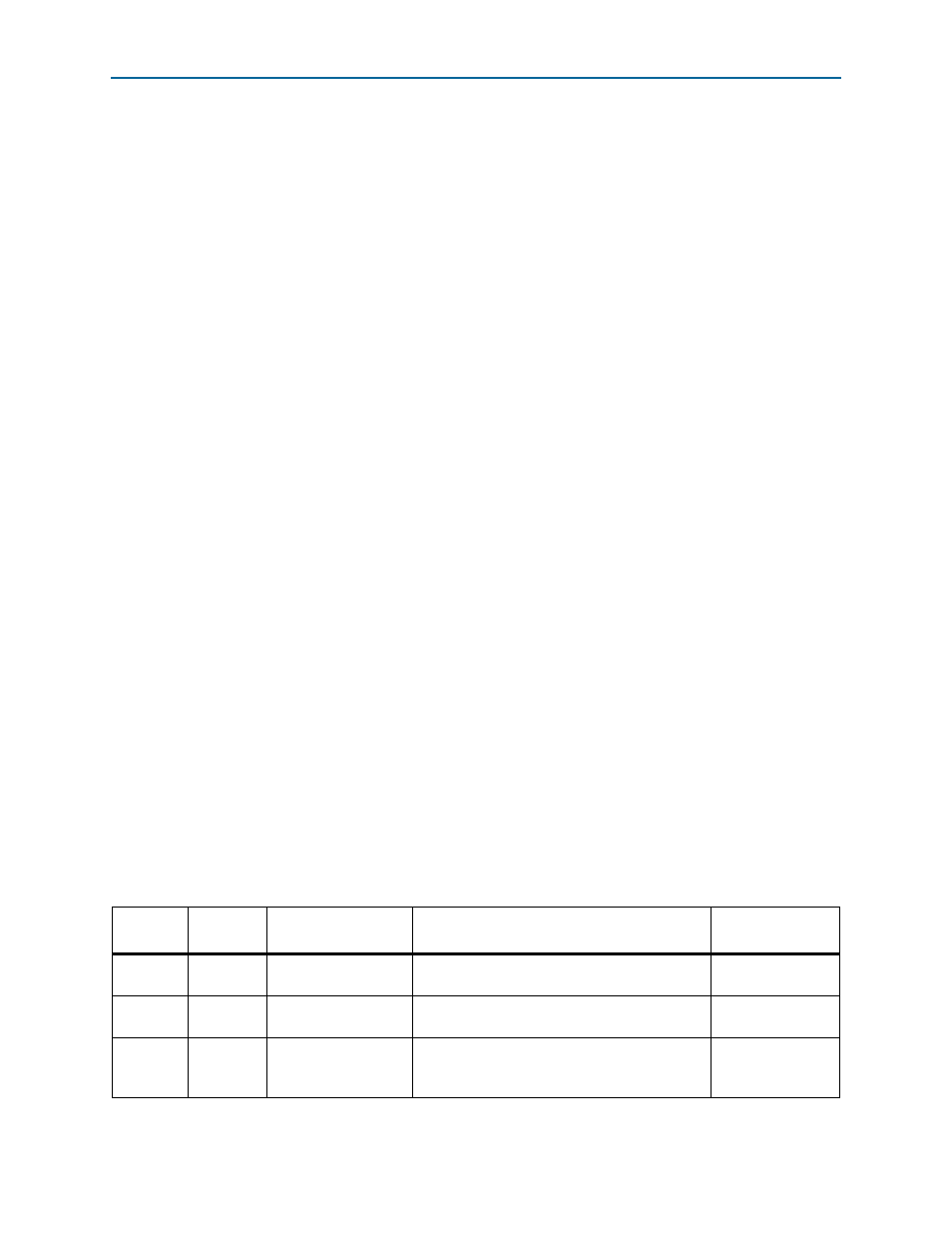

Table 7–1. Testbench Registers (Part 1 of 2)

Module

Register

Address

Register Name

Description

Value

rio

0x00060

Base

Device ID CSR

Program the DUT to have an 8-bit base device ID

of 0xAA or a 16-bit device ID of 0xAAAA.

32'h00AA_FFFF

or

32’h00FF_AAAA

rio

0x0013C

General

Control

CSR

Enable Request packet generation by the DUT.

32'h6000_0000

sister_rio

0x00060

Base

Device ID CSR

Program the sister_rio module to have an 8-bit

base device ID of 0x55 or a 16-bit device ID of

0x5555

.

32'h0055_FFFF

or

32’h00FF_5555