Altera RapidIO MegaCore Function User Manual

Page 33

Chapter 2: Getting Started

2–11

Instantiating Multiple RapidIO IP Cores

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

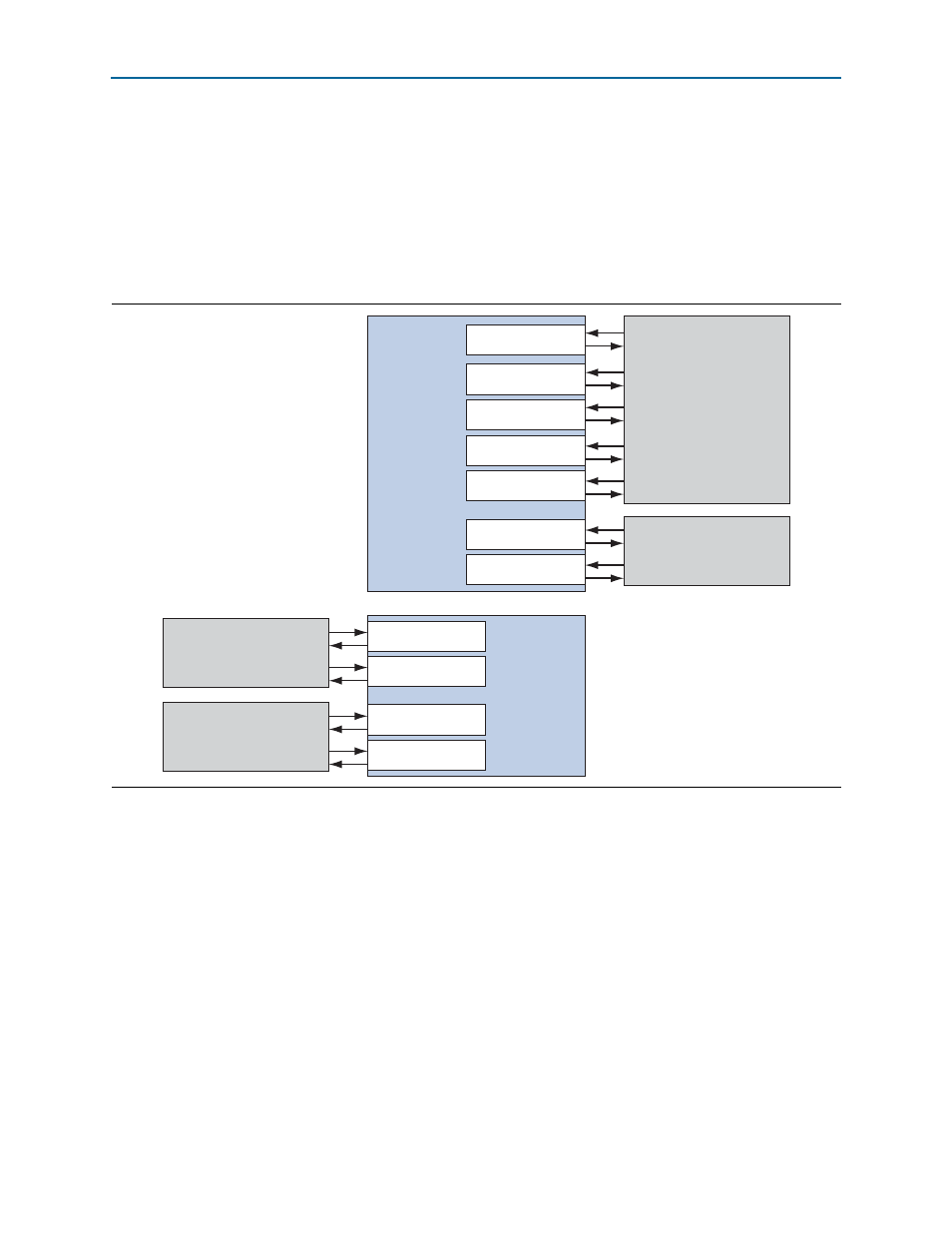

illustrates an example design with two Transceiver Reconfiguration

Controllers and four RapidIO IP cores. In the example, Altera Transceiver

Reconfiguration Controller 0 has seven reconfiguration interfaces, and Altera

Transceiver Reconfiguration Controller 1 has four reconfiguration interfaces. Each

sub-block shown in a Transceiver Reconfiguration Controller block represents a single

reconfiguration interface. The example shows only one possible configuration for this

combination of RapidIO IP cores; subject to the constraints described, you may choose

a different configuration.

Refer to

for the values of N and M in

f

Refer to the "Transceiver Reconfiguration Controller

for more information about the Transceiver Reconfiguration

Controller interfaces and how to control dynamic reconfiguration for multiple

transceiver channels. Refer to

for information about the

reconfig_fromgxb

and reconfig_togxb signals that connect a single RapidIO IP core

to multiple Transceiver Reconfiguration Controller interfaces of the same Transceiver

Reconfiguration Controller.

To enable the Quartus II software to place distinct RapidIO IP cores in the same

Arria V, Cyclone V, or Stratix V transceiver block, you must ensure that the

phy_mgmt_clk

input to each RapidIO IP core is driven by the same programming

interface clock.

Figure 2–3. Example Connections Between Two Transceiver Reconfiguration Controllers and Four RapidIO IP Cores

Altera

Transceiver

Reconfiguration

Controller

0

1x RapidIO

IP Core

1x RapidIO

IP Core

Altera

Transceiver

Reconfiguration

Controller

1

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_fromgxb[N-1:0]

reconfig_togxb[M-1:0]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_fromgxb[2N-1:N]

reconfig_togxb[2M-1:M]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_fromgxb[N-1:0]

reconfig_togxb[M-1:0]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_from_xcvr[N-1:0]

reconfig_to_xcvr[M-1:0]

reconfig_fromgxb[2N-1:N]

reconfig_togxb[2M-1:M]

1x RapidIO

IP Core

reconfig_fromgxb[N-1:0]

reconfig_togxb[M-1:0]

reconfig_fromgxb[2N-1:N]

reconfig_togxb[2M-1:M]

4x RapidIO

IP Core

reconfig_fromgxb[5N-1:4N]

reconfig_togxb[5M-1:4M]

reconfig_fromgxb[3N-1:2N]

reconfig_togxb[3M-1:2M]

reconfig_fromgxb[4N-1:3N]

reconfig_togxb[4M-1:3M]

reconfig_fromgxb[N-1:0]

reconfig_togxb[M-1:0]

reconfig_fromgxb[2N-1:N]

reconfig_togxb[2M-1:M]