Status packet and error monitoring signals, Status packet and error monitoring signals –2, Refer to – Altera RapidIO MegaCore Function User Manual

Page 116

5–2

Chapter 5: Signals

Physical Layer Signals

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

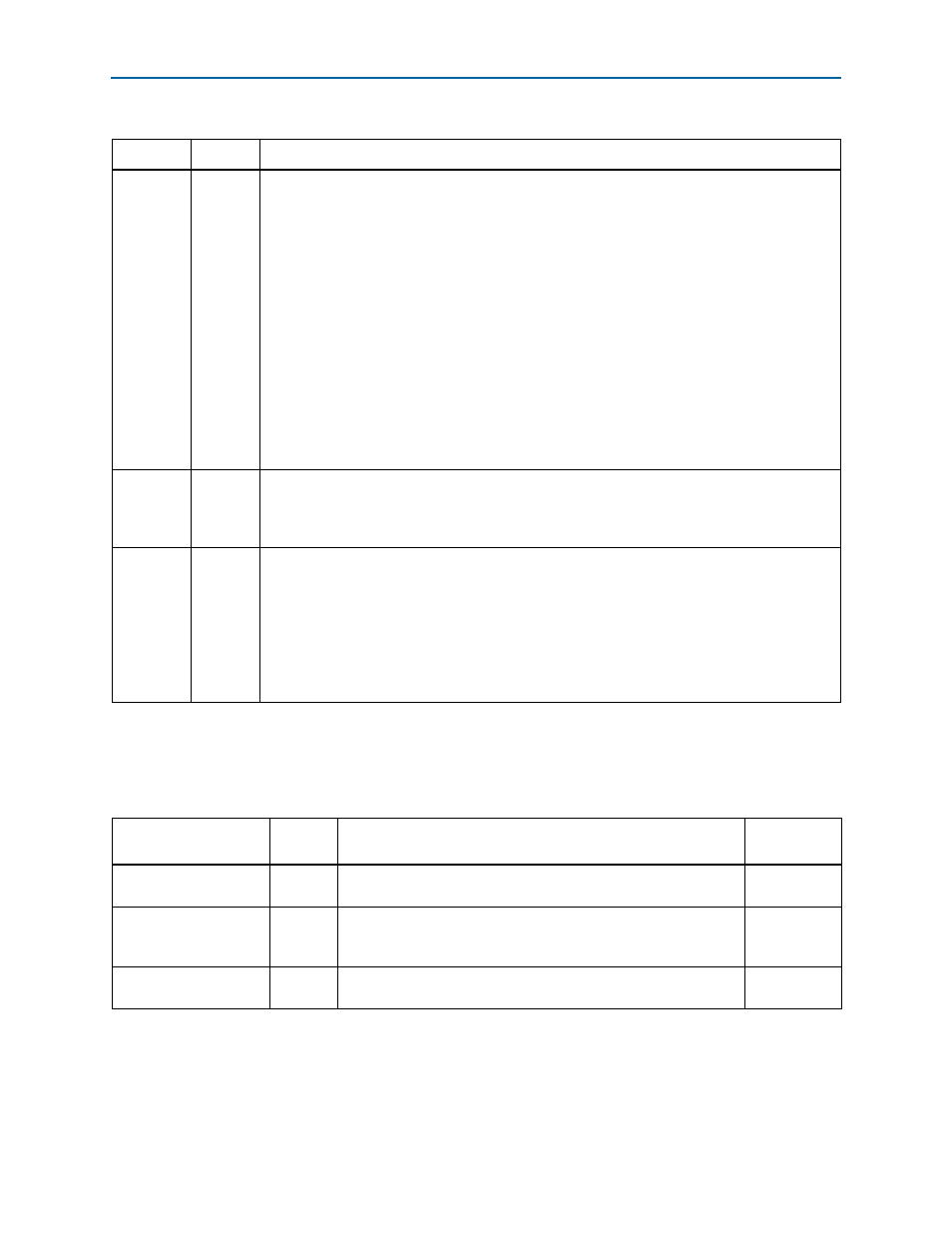

Status Packet and Error Monitoring Signals

lists the status packet and error monitoring signals.

Table 5–3. Global Signals

Signal

Direction

Description

reset_n

Input

Active-low system reset. In variations that implement only the Physical layer, this reset signal is

associated with the reference clock. In variations with a Transport layer this reset is associated

with the Avalon system clock.

reset_n

can be asserted asynchronously, but must stay asserted at least one clock cycle and

must be de-asserted synchronously with the clock with which it is associated. Refer to

for a circuit that shows how to enforce synchronous deassertion of reset_n.

Altera recommends that you apply an explicit 1 to 0 transition on the reset_n input port in

simulation, to ensure that the simulation model is properly reset.

In the Qsys flow, this signal is named clock_reset by default.

In Arria V, Cyclone V, and Stratix V devices, the reset_n signal must be asserted synchronously

with the embedded PHY IP core phy_mgmt_clk_reset signal described in

Table 5–8 on

page 5–4

. Refer to

for a circuit that shows how to enforce all of the reset

clocking requirements in Arria V, Cyclone V, and Stratix V devices. In addition, reset_n should

not be deasserted when the Altera Transceiver Reconfiguration Controller reconfig_busy signal

is high.

rxclk

Output

Receive-side recovered clock. This signal is derived from the rxgxbclk clock—a clock driven by

the transceiver—by division by 1 or 2, depending on the configuration of the IP core. For the

frequency of this clock for each baud rate and mode, refer to

.

txclk

Output

The internal clock of the Physical layer. This signal is derived from the txgxbclk clock—a clock

driven by the transceiver—by division by 1 or 2, depending on the configuration of the IP core. For

the frequency of this clock for each baud rate and mode, refer to

.

This clock runs reliably only after the transceiver transmitter PLL is locked to the reference clock,

which you can detect by monitoring the gxbpll_locked signal (refer to

Table 5–8 on page 5–4

).

If you use this clock to drive the Avalon system clock, you must ensure you do not deassert

reset_n

before gxbpll_locked is asserted.

Table 5–4. Status Packet and Error Monitoring (Part 1 of 2)

Output Signal

Clock

Domain

Description

Exported by

Qsys

packet_transmitted

txclk

Pulsed high for one clock cycle when a packet’s transmission

completes normally.

yes

packet_cancelled

txclk

Pulsed high for one clock cycle when a packet’s transmission is

cancelled by sending a stomp, a restart-from-retry, or a link-

request

control symbol.

yes

packet_accepted

rxclk

Pulsed high for one clock cycle when a packet-accepted control

symbol is being transmitted.

yes