Register-related signals, Transport and logical layer signals, Avalon-mm interface signals – Altera RapidIO MegaCore Function User Manual

Page 124: Register-related signals –10, Transport and logical layer signals –10, Avalon-mm interface signals –10

5–10

Chapter 5: Signals

Transport and Logical Layer Signals

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

f

For more information, refer to

device handbook. For more information about offset cancellation, refer to the relevant

device handbook.

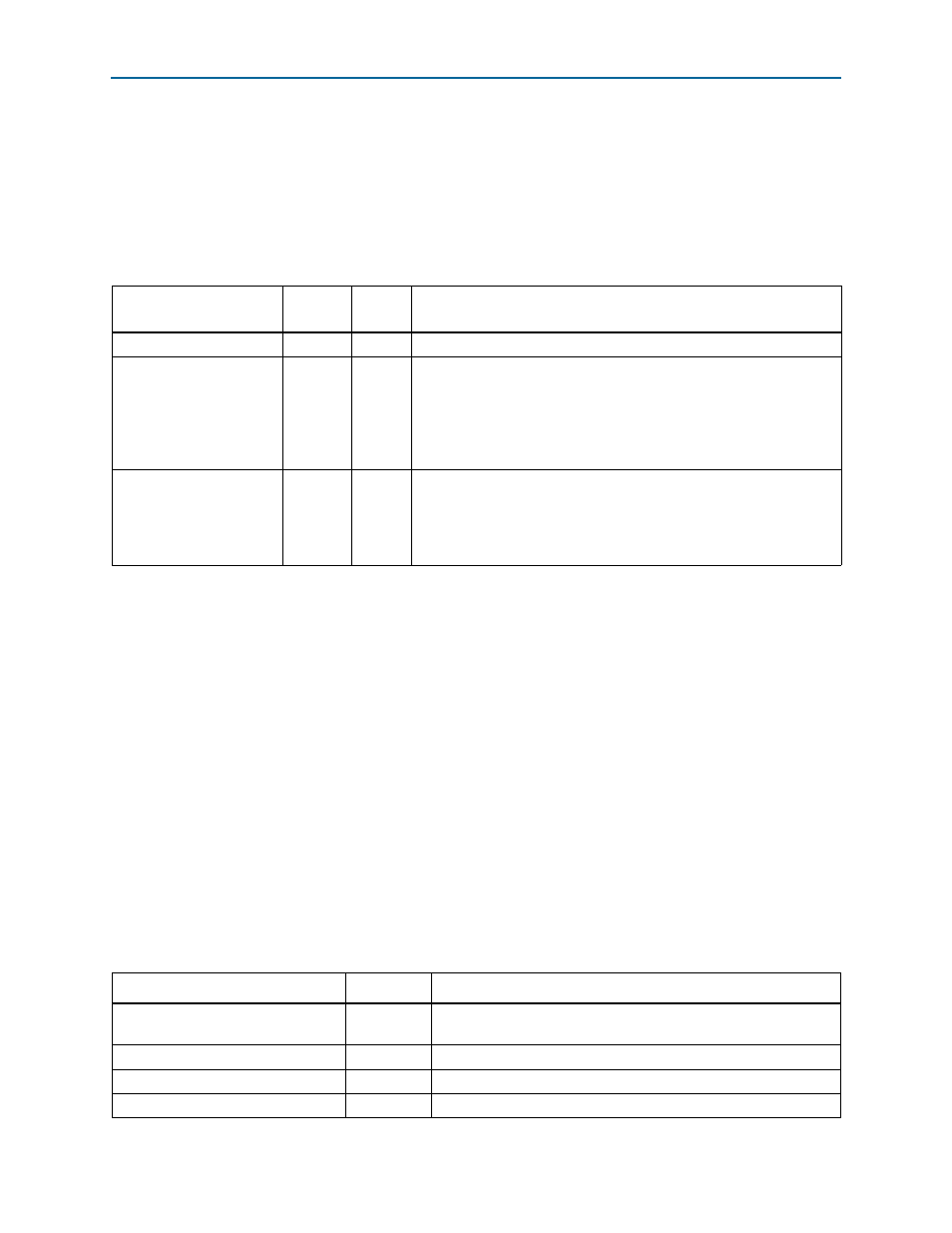

Register-Related Signals

Table 5–10

lists the register-related signals.

Transport and Logical Layer Signals

through

list the signals used by the Transport layer and the

Maintenance, Input/Output, and Doorbell Logical layer modules of the RapidIO IP

core. For a list of descriptions of the pins and signals used and generated by the

Physical layer, including the RapidIO IP core clock signals, refer to

Avalon-MM Interface Signals

through

list the standard signals for the Avalon-MM interfaces.

Signals on Avalon-MM interfaces are in the Avalon system clock domain.

1

When you instantiate the IP core in Qsys, these signals are automatically connected

and are not visible as inputs or outputs of the system.

f

for details.

Table 5–10. Register-Related Signals

Signal

Direction

Clock

Domain

Description

ef_ptr[15:0]

Input

txclk

Most significant bits [31:16] of the PHEAD0 register.

master_enable

Output

txclk

This output reflects the value of the Master Enable bit of the Port

General

Control CSR, which indicates whether this device is allowed

to issue request packets. If the Master Enable bit is not set, the device

may only respond to requests. User logic connected to the Avalon-ST

pass-through interface should honor this value and not cause the

Physical layer to issue request packets when it is not allowed.

port_response_timeout

[23:0]

Output

txclk

Most significant bits [31:8] of PRTCTRL register. User logic connected to

the pass-through interface that results in request packets requiring a

response can use this value to check for request to response time-out.

This signal is present in variations that include the Avalon-ST

pass-through interface.

Table 5–11. System Maintenance Avalon-MM Slave Interface Signals (Part 1 of 2)

Signal

Direction

Description

sys_mnt_s_clk

Input

This signal is not used, therefore it can be left open. The Avalon

clock is used internally to sample this interface.

sys_mnt_s_chipselect

Input

System maintenance slave chip select

sys_mnt_s_waitrequest

Output

System maintenance slave wait request

sys_mnt_s_read

Input

System maintenance slave read enable