Input/output avalon-mm master module, Input/output avalon-mm master module –34 – Altera RapidIO MegaCore Function User Manual

Page 80

4–34

Chapter 4: Functional Description

Logical Layer Modules

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

■

“Input/Output Avalon-MM Master Module”

■

“Input/Output Avalon-MM Slave Module” on page 4–41

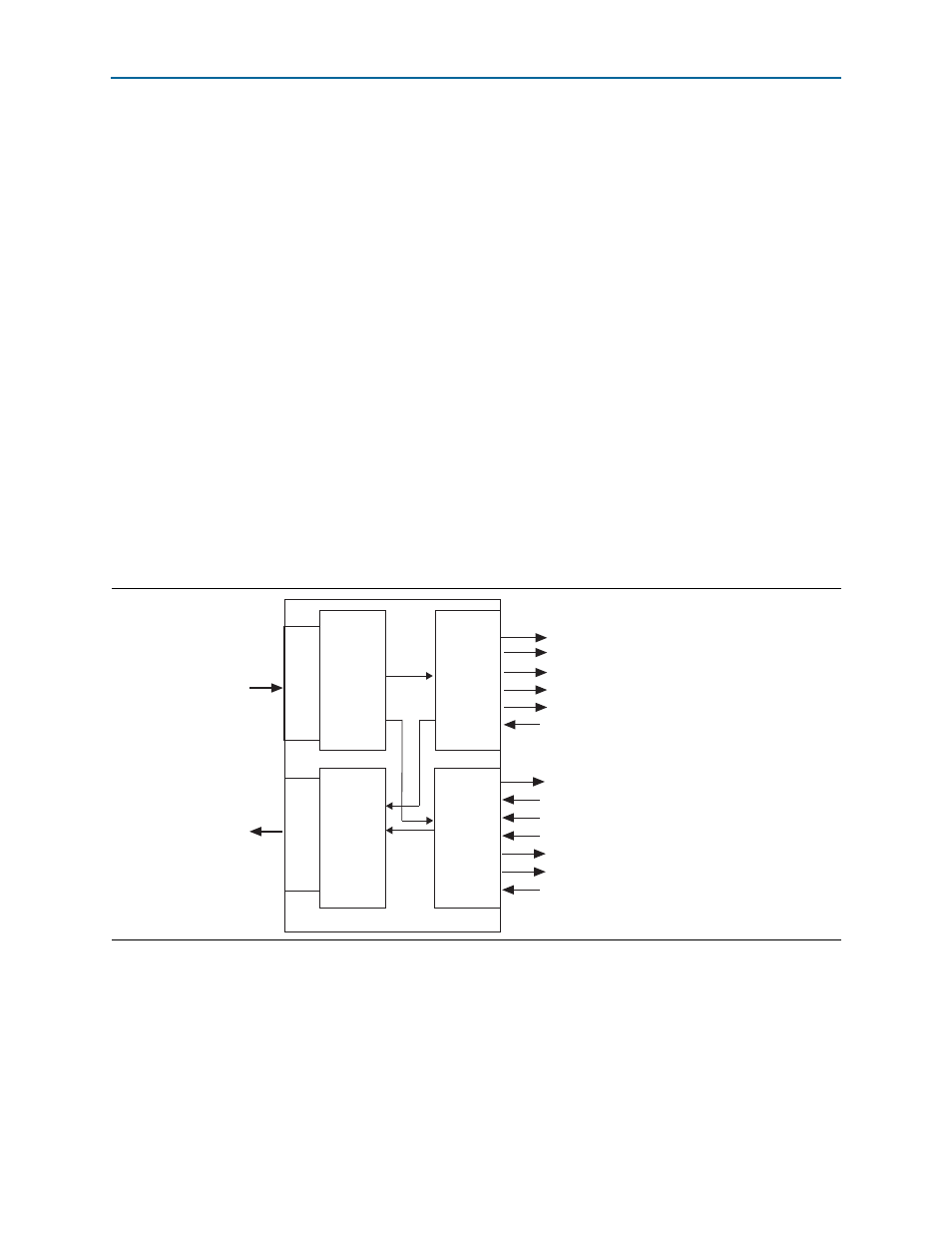

Input/Output Avalon-MM Master Module

The Input/Output (I/O) Avalon-MM master Logical layer module receives RapidIO

read and write request packets from a remote endpoint through the Transport layer

module. The I/O Avalon-MM master module translates the request packets into

Avalon-MM transactions, and creates and returns RapidIO response packets to the

source of the request through the Transport layer.

shows a block diagram

of the I/O Avalon-MM master Logical module and its interfaces.

1

The I/O Avalon-MM master module is referred to as a master module because it is an

Avalon-MM interface master.

To maintain full-duplex bandwidth, two independent Avalon-MM interfaces are used

in the I/O master module—one for read transactions and one for write transactions.

The I/O Avalon-MM master module can process a mix of as many as seven NREAD or

NWRITE_R

requests simultaneously. If the Transport layer module receives an NREAD or

NWRITE_R

request packet while seven requests are already pending in the I/O

Avalon-MM master module, the new packet remains in the Transport layer until one

of the pending transactions completes.

Figure 4–17. I/O Master Block Diagram

Transport Side

TX

Interface

32 or 64 bits

Transport Side

RX

Interface

32 or 64 bits

Tx

Sink

Source

Read

Master

Write

Master

io_m_rd_readdata

io_m_rd_readdatavalid

io_m_rd_read

io_m_rd_waitrequest

io_m_rd_address

io_m_rd_burstcount

io_m_rd_readerror

io_m_wr_writedata

io_m_wr_write

io_m_wr_waitrequest

io_m_wr_address

io_m_wr_burstcount

io_m_wr_ byteenable

Rx

Datapath Read

Avalon-MM Interface

32 or 64 bits

Datapath Write

Avalon-MM Interface

32 or 64 bits