Reset for rapidio ip cores, General rapidio reset signal requirements, Reset for rapidio ip cores –7 – Altera RapidIO MegaCore Function User Manual

Page 53: General rapidio reset signal requirements –7

Chapter 4: Functional Description

4–7

Clocking and Reset Structure

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

Reset for RapidIO IP Cores

The RapidIO IP core has the following reset input signals:

■

reset_n: m

ain active-low reset signal

■

phy_mgmt_clk_reset: t

ransceiver software management interface signal to reset

the Custom PHY IP core included in the RapidIO Arria V, Cyclone V, or Stratix V

variation (Arria V, Cyclone V, and Stratix V variations only)

■

tx_analogreset

, rx_analogreset, tx_digitalreset, rx_digitalreset:

transceiver reset signals (Arria 10 variations only)

In addition, if you turn on Enable transceiver dynamic reconfiguration for your

RapidIO Arria 10 variation, the IP core includes reconfig_reset_chN input clock to

reset the

an Arria 10 Native PHY dynamic reconfiguration interface for each

RapidIO lane N.

General RapidIO Reset Signal Requirements

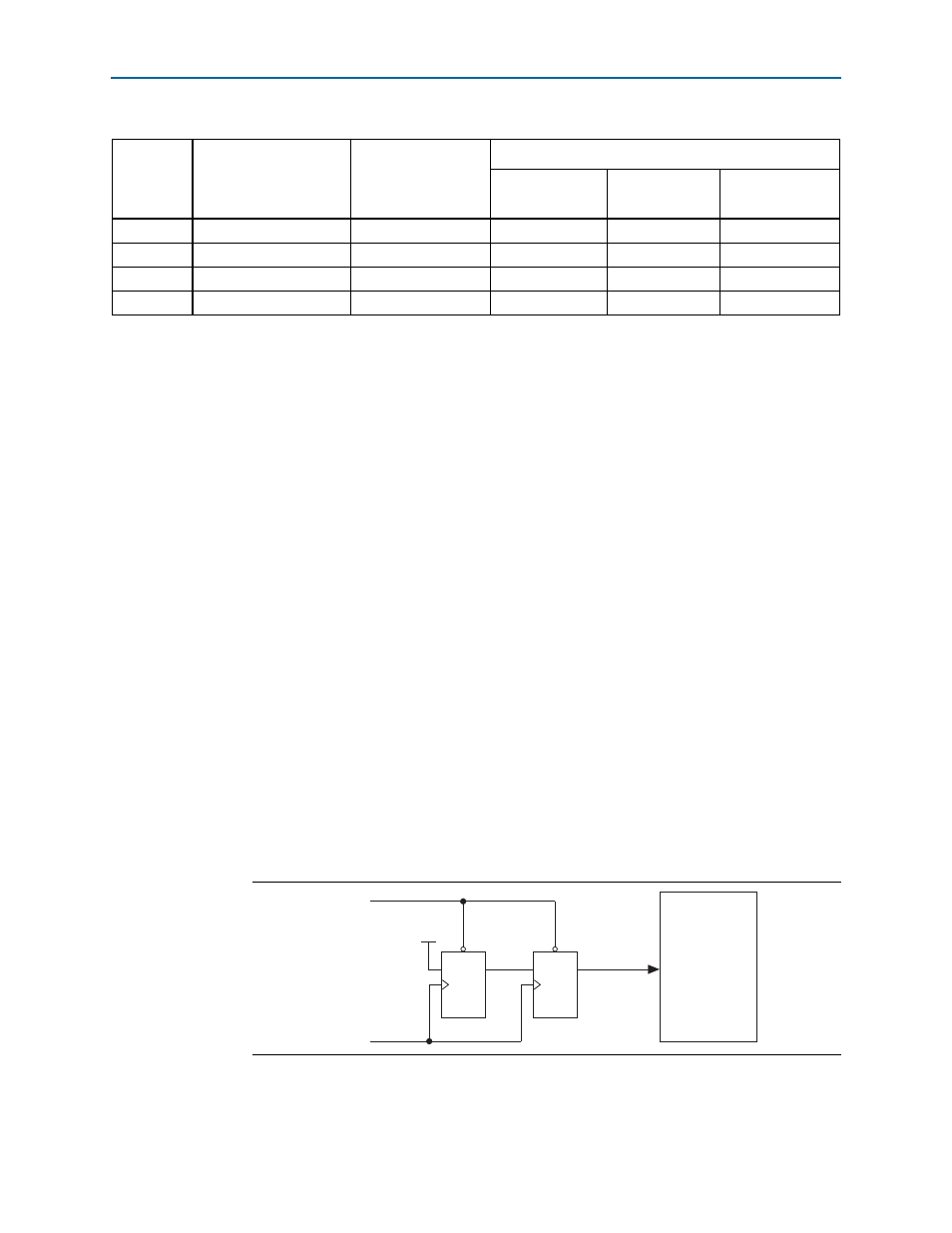

All reset signals can be asserted asynchronously to any clock. However, most reset

signals must be deasserted synchronously to a specific clock.

The reset_n input signal can be asserted asynchronously, but must last at least one

Avalon system clock period and be deasserted synchronously to the rising edge of the

Avalon system clock.

Figure 4–3

shows a circuit that ensures these conditions.

Table 4–3. Clock Frequencies for 4x RapidIO IP Core Variations

Baud Rate

(Gbaud)

txclk, rxclk, and

default reference clock

frequency

(1)

(MHz)

rxgxbclk

Avalon System Clock (sysclk)

Minimum (MHz)

Typical

(MHz)

Maximum

(2)

(MHz)

1.25

62.5 62.5

31.25

62.5

93.75

2.5 125

125

62.5

125

187.5

3.125 156.25

156.25

78.125

156.25

234.275

5.0

250

250

125.0

250

250

Notes to

Table 4–3

:

(1) For information about the allowed reference clock frequencies, refer to

.

(2) The maximum system clock frequency might be limited by the achievable f

MAX

and can vary based on the family and speed grade.

Figure 4–3. Circuit to Ensure Synchronous Deassertion of reset_n

D

D

Q

Q

rst_n

rst_n

V

CC

sysclk

rst_n

reset_n

RapidIO

IP Core