Altera RapidIO MegaCore Function User Manual

Page 89

Chapter 4: Functional Description

4–43

Logical Layer Modules

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

■

The Input/Output Slave RapidIO Write Requests register described in

holds a count of the RapidIO write request packets that

have been transferred to the Transport layer.

■

The Input/Output Slave Pending NWRITE_R Transactions register described in

holds a count of the NWRITE_R requests that have been

issued but have not yet completed.

In addition, the NWRITE_RS_COMPLETED bit of the Input/Output Slave Interrupt

Enable

register described in

controls a maskable interrupt in

the Input/Output Slave Interrupt register described in

can be generated when the final pending NWRITE_R transaction completes.

You can use these registers to determine if a specific I/O write transaction has been

issued or if a response has been received for any or all issued NWRITE_R requests.

Input/Output Avalon-MM Slave Address Mapping Windows

Address mapping or translation windows map windows of 32-bit Avalon-MM

addresses to windows of 34-bit RapidIO addresses, and are defined by sets of the

32-bit registers in

A base register, a mask register, and an offset register define a window. The control

register stores information used to prepare the packet header on the RapidIO side of

the transaction, including the target device’s destination ID, the request packet's

priority, and selects between the three available write request packet types: NWRITE,

NWRITE_R

and SWRITE.

illustrates this address mapping.

You can change the values of the window-defining registers at any time, even after

sending a request packet and before receiving its response packet. However, you

should disable a window before changing its window-defining registers. A window is

enabled if the window enable (WEN) bit of the Input/Output Slave Mapping Window n

Mask

register is set, where n is the number of the transmit address translation window.

The number of mapping windows is defined by the parameter Number of transmit

address translation windows

; up to 16 windows are supported. Each set of registers

supports one external host or entity at a time. Your variation must have at least one

translation window. Arria 10 variations have 16 transmit address translation

windows.

For each window that is enabled, the least significant bits of the Avalon-MM address

are masked out by the window mask and the resulting address is compared to the

window base. If the addresses match, the RapidIO address in the outgoing request

packet is made of the least significant bits of the Avalon-MM address and the window

offset using the following equation:

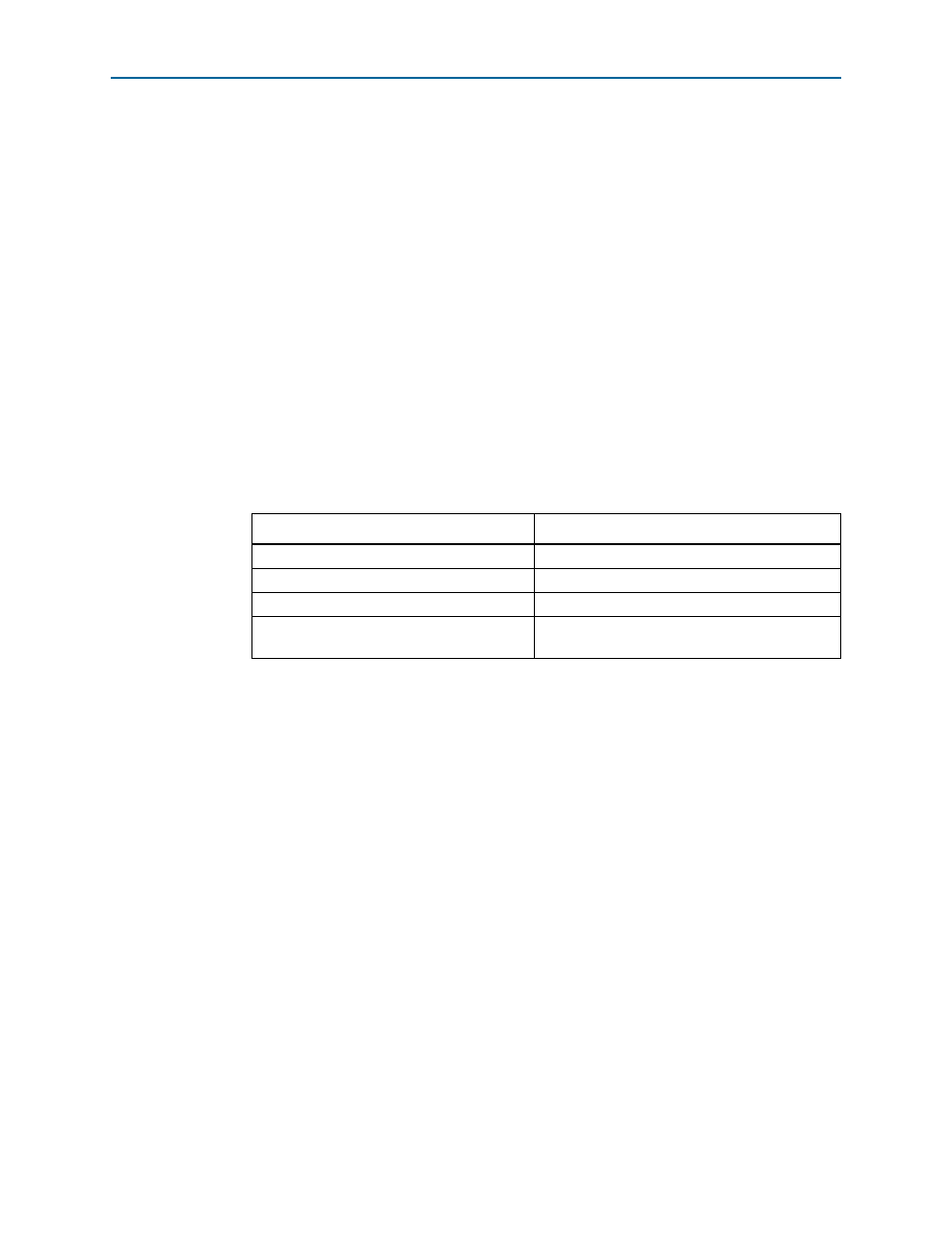

Table 4–10. Address Mapping and Translation Registers

Registers

Location

Input/Output slave base address

Input/Output slave address mask

Input/Output slave address offset

Input/Output slave packet control information

(for packet header)