Altera RapidIO MegaCore Function User Manual

Page 120

5–6

Chapter 5: Signals

Physical Layer Signals

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

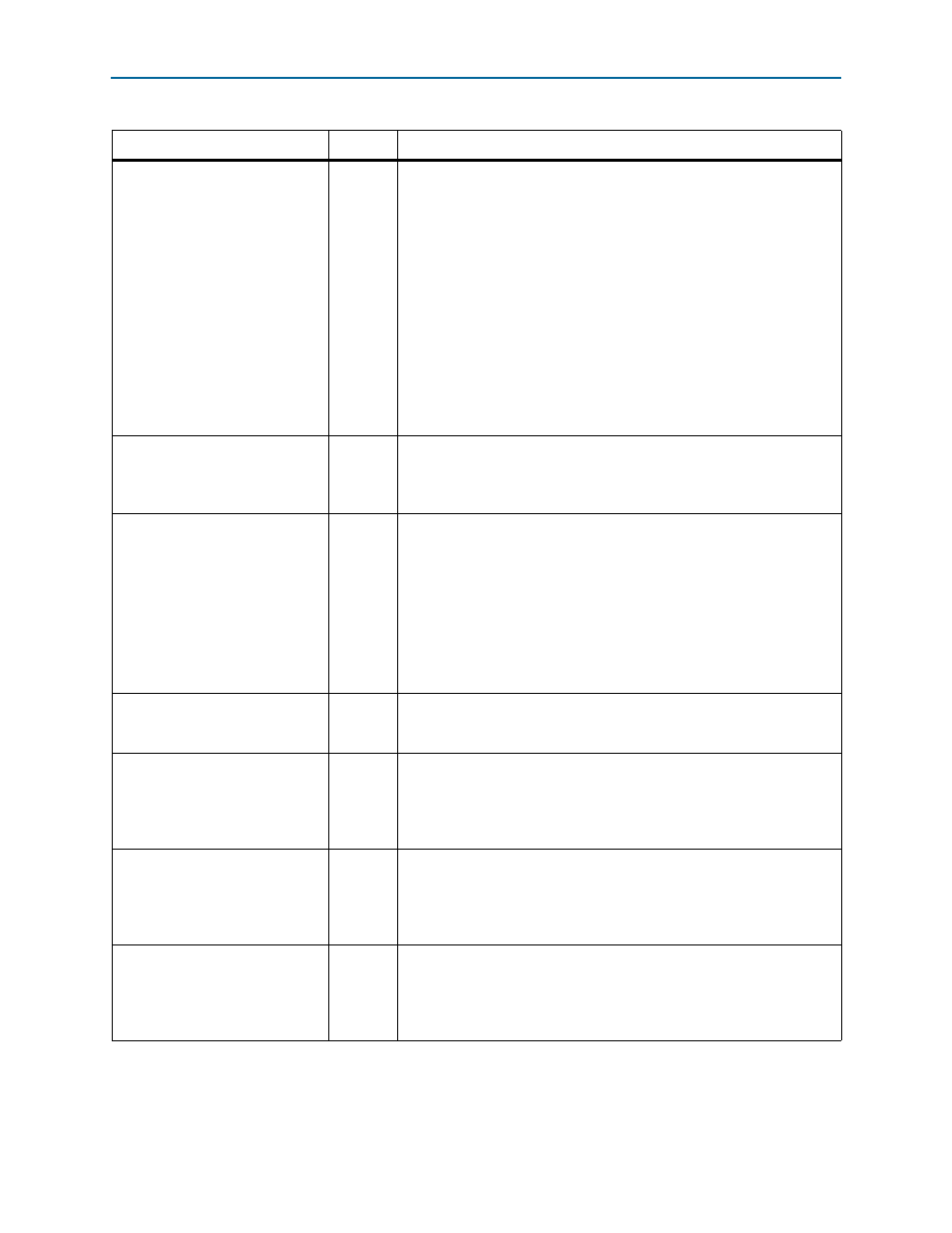

reconfig_fromgxb

(2)

Output

Driven to an external dynamic reconfiguration block. The bus identifies the

transceiver channel whose settings are being transmitted to the dynamic

reconfiguration block. If no external dynamic reconfiguration block is

used, then this output bus can be left unconnected. However, not using a

dynamic reconfiguration block that enables offset cancellation results in a

non-functional hardware design.

In Arria V, Cyclone V, and Stratix V devices, the width of this bus is (C + 1)

× 46, where C is the number of channels, 1, 2, or 4. This width supports

communication from the transceiver to C + 1 reconfiguration interfaces in

an Altera Reconfiguration Controller, one interface dedicated to each

channel and an additional interface for the transceiver PLL.

For more information about the Altera Reconfiguration Controller

component, refer to

.

This signal is not present in Arria 10 variations.

gxbpll_locked

Output /

Input

Indicates the transceiver transmitter PLL is locked to the reference clock.

In Arria 10 variations, this is an input signal to the RapidIO IP core that is

intended to be connected to the external PLL; in all other variations, this is

an output signal from the transceiver PLL in the RapidIO IP core.

gxb_powerdown

Input

Transceiver block reset and power down. This resets and powers down all

circuits in the transceiver block. This signal does not affect the refclk

buffers and reference clock lines.

All the gxb_powerdown input signals of IP cores intended to be placed in

the same quad should be tied together. The gxb_powerdown should be

tied low or should remain asserted for at least 2 ms whenever it is

asserted.

This signal is not present in Arria V, Arria 10, Cyclone V, or Stratix V

variations.

rx_errdetect

Output

Transceiver 8B10B code group violation signal bus. The signal width

depends on the IP core mode. For details, refer to the relevant device

handb

.

tx_bonding_clocks_ch0[5:0]

Input

Transceiver channel TX input clocks for RapidIO lane 0. This signal is

available only in Arria 10 variations. Each transceiver channel that

corresponds to a RapidIO lane has six input clock bits. The bits are

expected to be driven from a TX PLL. Refer to

tx_bonding_clocks_ch1[5:0]

Input

Transceiver channel TX input clocks for RapidIO lane 1. This signal is

available only in Arria 10 2x and 4x variations. Each transceiver channel

that corresponds to a RapidIO lane has six input clock bits. The bits are

expected to be driven from a TX PLL. Refer to

tx_bonding_clocks_ch2[5:0]

Input

Transceiver channel TX input clocks for RapidIO lane 2. This signal is

available only in Arria 10 4x variations. Each transceiver channel that

corresponds to a RapidIO lane has six input clock bits. The bits are

expected to be driven from a TX PLL. Refer to

Table 5–8. Transceiver Signals (Part 3 of 4)

Signal Direction

Description