Reference clock, Reference clock –4 – Altera RapidIO MegaCore Function User Manual

Page 50

4–4

Chapter 4: Functional Description

Clocking and Reset Structure

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

1

You must drive the Avalon system clock from a clock source that is running reliably

when the RapidIO IP core comes out of reset.

Reference Clock

The reference clock signal drives the transceiver and the Physical layer. By default,

this clock is called clk in the generated IP core. Qsys allows you to export the clk

signal with a name of your choice.

The reference clock, clk, is the incoming reference clock for the transceiver’s PLL. The

frequency of the input clock must match the value you specify for the Reference clock

frequency

parameter. The transceiver PLL converts the reference clock frequency to

the internal clock speed that supports the RapidIO IP core baud rate.

The RapidIO parameter editor lets you select one of the supported frequencies. The

selection allows you to use an existing clock in your system as the reference clock for

the RapidIO IP core.

1

You must drive the external transceiver TX PLL pll_refclk0 input clock from the

same source from which you drive the RapidIO IP core clk input clock.

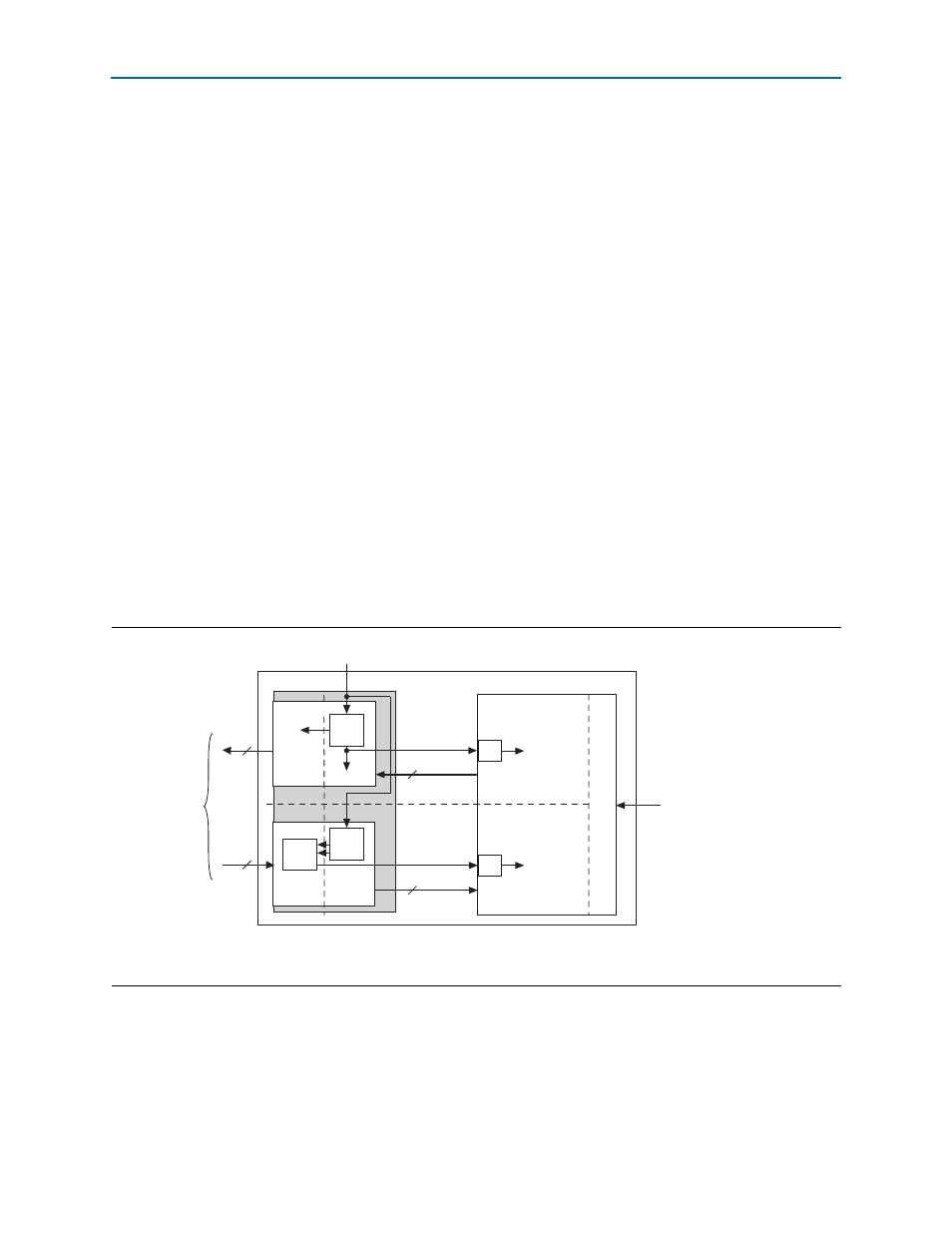

shows how the transceiver uses the reference clock in non-Arria 10

variations. In Arria 10 variations, clk is the reference clock only for the RX PLL. In

these variations, the reference clock for the TX PLL is an input signal to the TX PLL IP

core that you connect to the RapidIO IP core. For Arria 10 variations, re

.

The PLL generates the high-speed transmit clock and the input clocks to the receiver

high-speed deserializer clock and recovery unit (CRU). The CRU generates the

recovered clock (rxclk) that drives the receiver logic.

Figure 4–1. Reference Clock in a non-Arria 10 RapidIO IP Core

Note to

(1) This figure does not show the Custom PHY IP core clock phy_mgmt_clk.

Avalon system clock

rd

td

Transceiver

RapidIO MegaCore function

Serial Interfaces

4

4

PLL

Receiver

txgxbclk

TX data

rxgxbclk

RX data

Reference

Clock

txclk

rxclk

PLL

CRU

Transmitter