Altera RapidIO MegaCore Function User Manual

Page 104

4–58

Chapter 4: Functional Description

Logical Layer Modules

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

In cycle 0, the user logic indicates to the RapidIO IP core that it is ready to receive a

packet transfer by asserting gen_rx_ready. In cycle 1, the IP core asserts gen_rx_valid

and gen_rx_startofpacket. During this cycle, gen_rx_size is valid and indicates that

five cycles are required to transfer the packet.

shows the RapidIO header

fields and the payload carried on the gen_rx_data bus in each cycle.

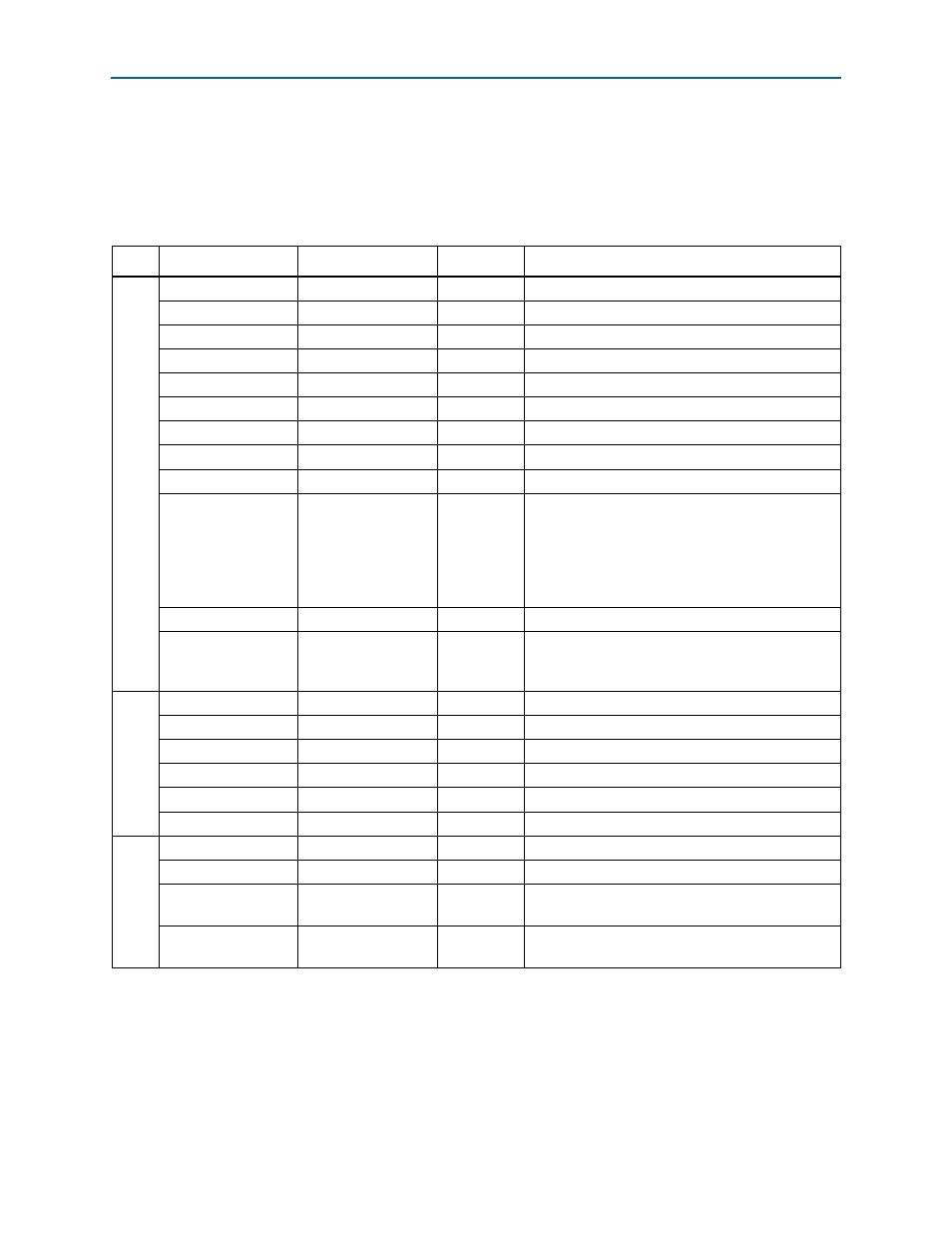

Table 4–15. RapidIO Header Fields and gen_rx_data Bus Payload (Part 1 of 2)

Cycle

Field

gen_rx_data bus

Value

Comment

1

ackID

[63:59]

5'h00

rsvd

[58:57]

2'h0

CRF

[56]

1'b0

prio

[55:54]

2'h0

tt

[53:52]

2'h0

Indicates 8-bit device IDs.

ftype

[51:48]

4'h5

A value of 5 indicates a Write Class packet.

destinationID

[47:40]

8'haa

sourceID

[39:32]

8'hcc

ttype

[31:28]

4'h4

The value of 4 indicates a NWRITE transaction.

wrsize

[27:24]

4'hc

The wrsize and wdptr values encode the

maximum size of the payload field. In this example,

they decode to a value of 32 bytes. For details, refer

to Table 4-4 in Part 1: Input/Output Logical

Specification of the RapidIO Interconnect

Specification, Revision 2.1

srcTID

[23:16]

8'h00

address[28:13]

[15:0]

16'h5a5a

The 29 bit address composed is

29’hb4b5959

.

This becomes

32'h5a5acac8

, the double-word

physical address.

2

address[12:0]

[63:51]

13'h1959

wdptr

[50]

1'b0

See description for the size field.

xamsbs

[49:48]

2'h0

Payload Byte0,1

[47:32]

16'h0001

Payload Byte2,3

[31:16]

16'h0203

Payload Byte4,5

[15:0]

16'h0405

3

Payload Byte6,7

[63:48]

16'h0607

Payload Byte8,9

[47:32]

16'h0809

Payload

Byte10,11

[31:16]

16'h0a0b

Payload

Byte12,13

[15:0]

16'h0c0d