Altera RapidIO MegaCore Function User Manual

Page 88

4–42

Chapter 4: Functional Description

Logical Layer Modules

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

An outbound request that requires a response—an NWRITE_R or an NREAD

transaction—is assigned a time-out value that is the sum of the VALUE field of the Port

Response Time-Out Control

register (

) and the current value of

a free-running counter. When the counter reaches the time-out value, if the transaction

has not yet received a response, the transaction times out. Refer to

information about the duration of the time-out.

If you turn off the I/O read and write order preservation option in the RapidIO

parameter editor, if a read and a write request arrive simultaneously or one clock

cycle apart on the Avalon-MM interfaces, the order of transaction completion is

undefined. However, if you turn on the I/O read and write order preservation option,

the read requests buffer and the write requests buffer shown in

are

combined, to preserve the relative order of read and write requests that appear on the

Avalon-MM interface. In Arria 10 variations, the read and write request buffers are

combined.

Keeping Track of I/O Write Transactions

The following three registers are available to software to keep track of I/O write

transactions:

■

The Input/Output Slave Avalon-MM Write Transactions register described in

holds a count of the write transactions that have been

initiated on the write Avalon-MM slave interface.

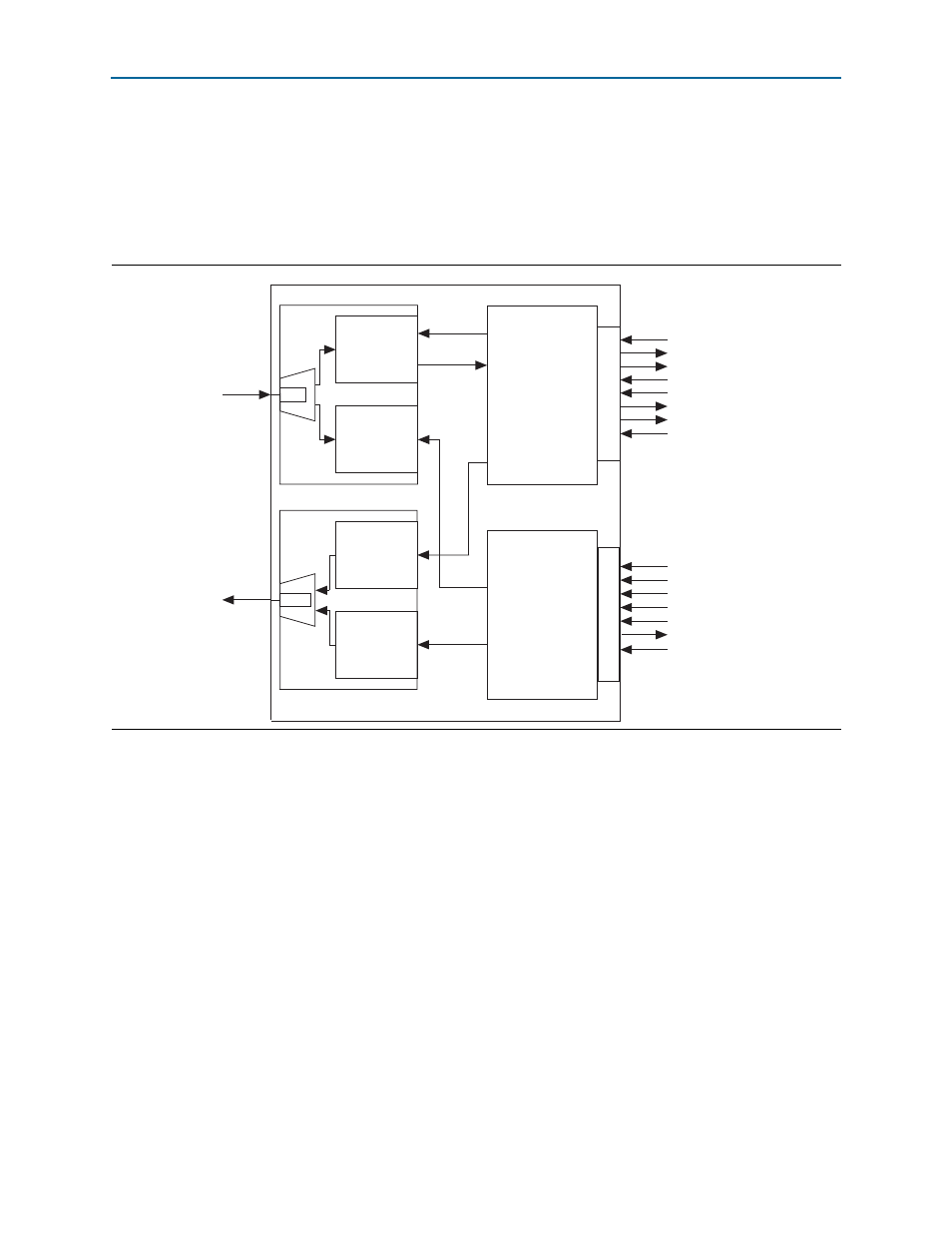

Figure 4–21. Input/Output Avalon-MM Slave Logical Layer Block Diagram

Data Path

Read

Avalon-MM Bus

32 of 64 bits

Pending Reads

Pending Writes

Read

Avalon-MM Slave

Write

Avalon-MM Slave

Read Request

Buffer

Write Request

Buffer

Tx Interface

From

Transport

Layer

To

Transport

Layer

Sink

Source

Data Path

Write

Avalon-MM Bus

32 of 64 bits

io_s_rd_read

io_s_rd_readdatavalid

io_s_rd_readdata

io_s_rd_address

io_s_rd_burstcount

io_s_rd_readerror

io_s_rd_waitrequest

io_s_wr_write

io_s_wr_writedata

io_s_wr_byteenable

io_s_wr_address

io_s_wr_burstcount

io_s_wr_waitrequest

io_s_wr_chipselect

io_s_rd_chipselect