Compiling the full design and programming the fpga – Altera RapidIO MegaCore Function User Manual

Page 31

Chapter 2: Getting Started

2–9

Compiling the Full Design and Programming the FPGA

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

explains these options.

f

For more information about timing analyzers, refer to the Quartus II Help and the

Timing Analysis section

of the Quartus II Handbook

.

Compiling the Full Design and Programming the FPGA

You can use the Start Compilation command on the Processing menu in the

Quartus II software to compile your design. After successfully compiling your design,

program the targeted Altera device with the Programmer and verify the design in

hardware.

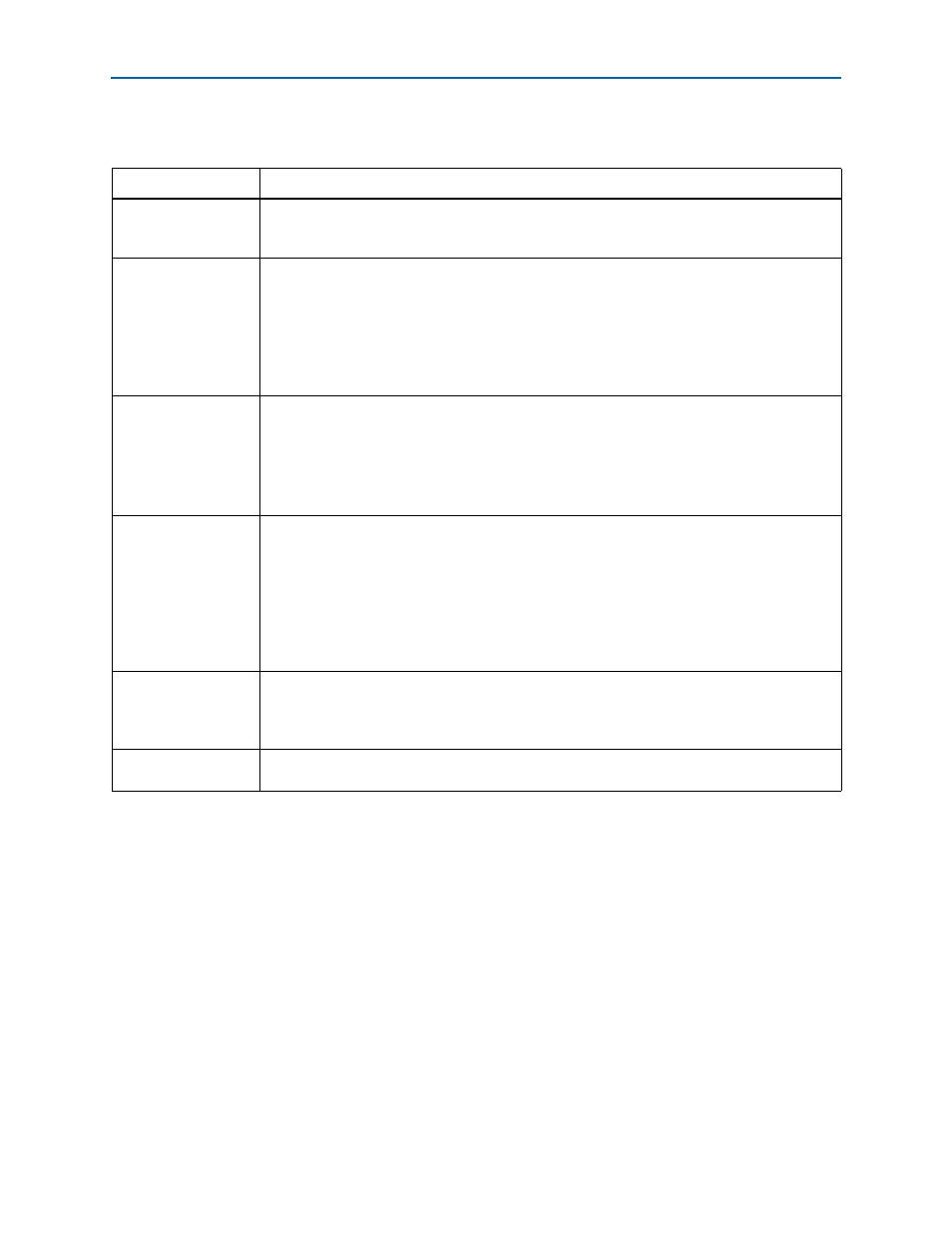

Table 2–2. add_rio_constraints Options

Constraint

Use

-no_compile

Use the -no_compile option to prevent analysis and synthesis. Use this option only if you

performed analysis and synthesis or fully compiled your project prior to using this script. Using

this option decreases turnaround time during development.

-ref_clk_name

The Rapid IO IP core has a top-level reference clock name clk. If, in Qsys, you rename this clock

or you connect the reference clock port of the IP core to a clock named something other than clk,

you must run the add_rio_constraints command with this option followed by the name of the

clock connected to the reference clock port of the RapidIO IP core. The following example

command illustrates the syntax:

add_rio_constraints -ref_clk_name CLK125

-sys_clk_name

By default, the Avalon system clock name used for the RapidIO IP core is named sysclk. If, in

Qsys, you rename this clock or connect it to a clock named something other than sysclk, you

must run the add_rio_constraints command with this option followed by the updated clock

name. The following example command illustrates the syntax:

add_rio_constraints -sys_clk_name CLK50

-phy_mgmt_clk_name

This option is available only for RapidIO variations that target an Arria V, Cyclone V, or Stratix V

device. By default, the PHY IP core management clock, which is present only in RapidIO variations

that target an Arria V, Cyclone V, or Stratix V device, is named phy_mgmt_clk. If, in Qsys, you

rename this clock or you connect it to a clock named something other than

<variation>_phy_mgmt_clk, you must run the add_rio_constraints command with this option

followed by the updated clock name. The following example command illustrates the syntax:

add_rio_constraints -phy_mgmt_clk_name CLK_PHY_MGMT

-patch_sdc

This option is only valid when used with the -ref_clk_name, -sys_clk_name, or

-phy_mgmt_clk

option. The -patch_sdc option patches the generated SDC script with the new

clock names. A back-up copy of the SDC script is created before the patch is made, and any edits

that were previously made to the SDC script are preserved.

-help

Use the -help option for information about the options used with the add_rio_constraints

command.