Altera RapidIO MegaCore Function User Manual

Page 73

Chapter 4: Functional Description

4–27

Logical Layer Modules

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

When you create your custom RapidIO IP core variation in the parameter editor, you

have the two or four choices for this module shown in

1

If you add this module to your non-Arria 10 variation and select an Avalon-MM

Slave

interface, you must also select a Number of Tx address translation windows. A

minimum of one window is required and a maximum of 16 windows are available.

Arria 10 variations have 16 Maintenance transmit address translation windows.

For more information, refer to

“Input/Output Maintenance Logical Layer Module”

shows a high-level block diagram of the Maintenance module and the

interfaces to other supporting modules. The Maintenance module can be segmented

into the following four major submodules:

■

Maintenance register

■

Maintenance slave processor

■

Maintenance master processor

■

Port-write processor

The following interfaces are supported:

■

Avalon-MM slave interface—User-exposed interface

■

Avalon-MM master interface—User-exposed interface

■

Tx interface—Internal interface used to communicate with the Transport layer

■

Rx interface—Internal interface used to communicate with the Transport layer

■

Register interface—Internal interface used to communicate with the Concentrator

Module

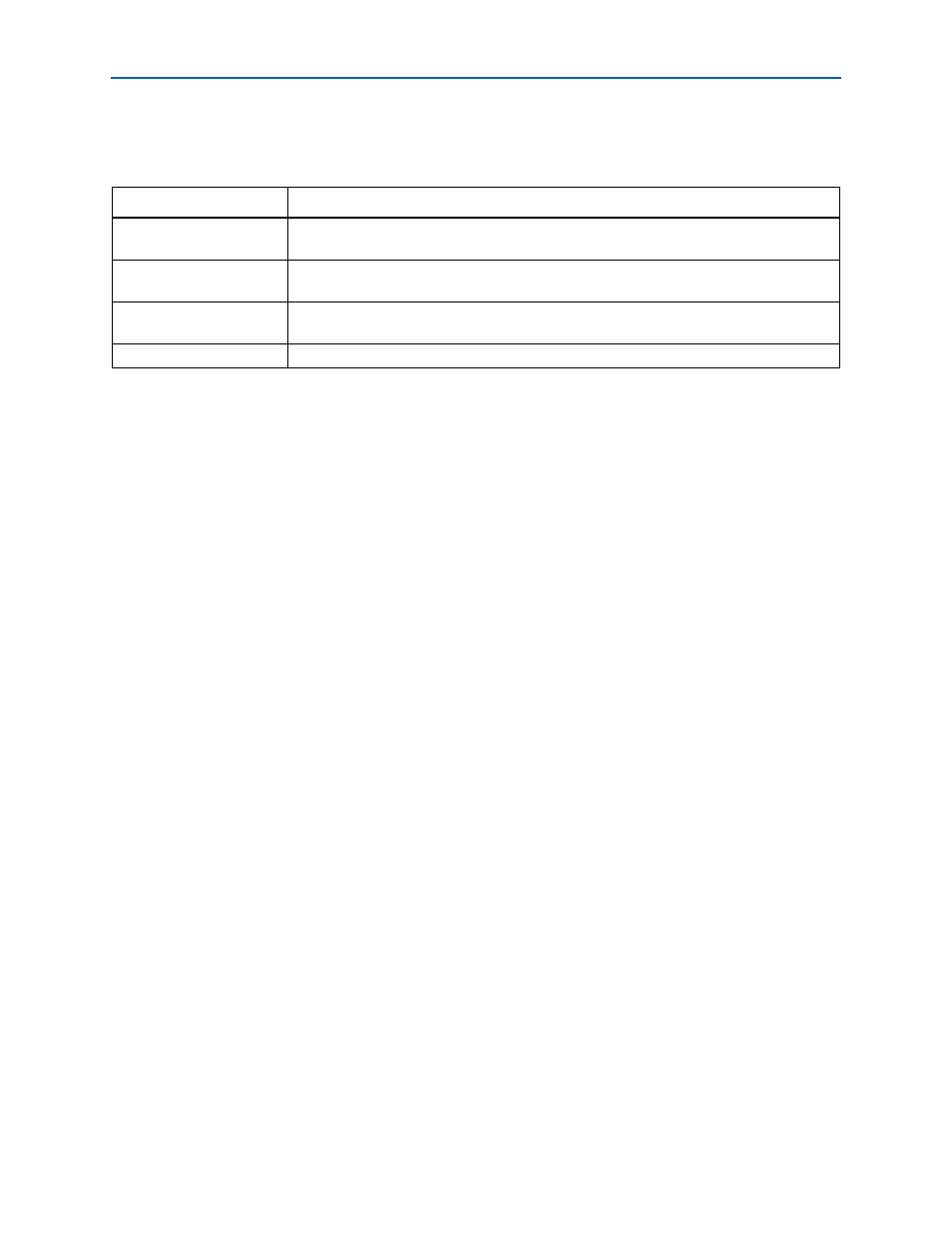

Table 4–5. Maintenance Logical Layer Interface Options

Option

Use

Avalon-MM Master and

Slave

Allows your IP core to initiate and terminate MAINTENANCE transactions.

Avalon-MM Master

Restricts your IP core to terminating MAINTENANCE transactions. This option is not available

for Arria 10 variations.

Avalon-MM Slave

Restricts your IP core to initiating MAINTENANCE transactions. This option is not available for

Arria 10 variations.

None

Prevents your IP core from initiating or terminating MAINTENANCE transactions.