Altera RapidIO MegaCore Function User Manual

Page 173

Chapter 7: Testbenches

7–11

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

The test iterates through these operations, each time incrementing the payload of the

port write. The loop exits when the max payload for a port-write has been transmitted,

64 bytes.

All of the operations in the loop are executed by running the rw_addr_data task either

in the bfm_cnt_master or the sister_bfm_cnt_master instances.

Transactions Across the Avalon-ST Pass-Through Interface

The demonstration testbench tests the Avalon-ST pass-through interface by

exchanging Type 9 (Data Streaming) traffic between the DUT and the sister_rio

module.

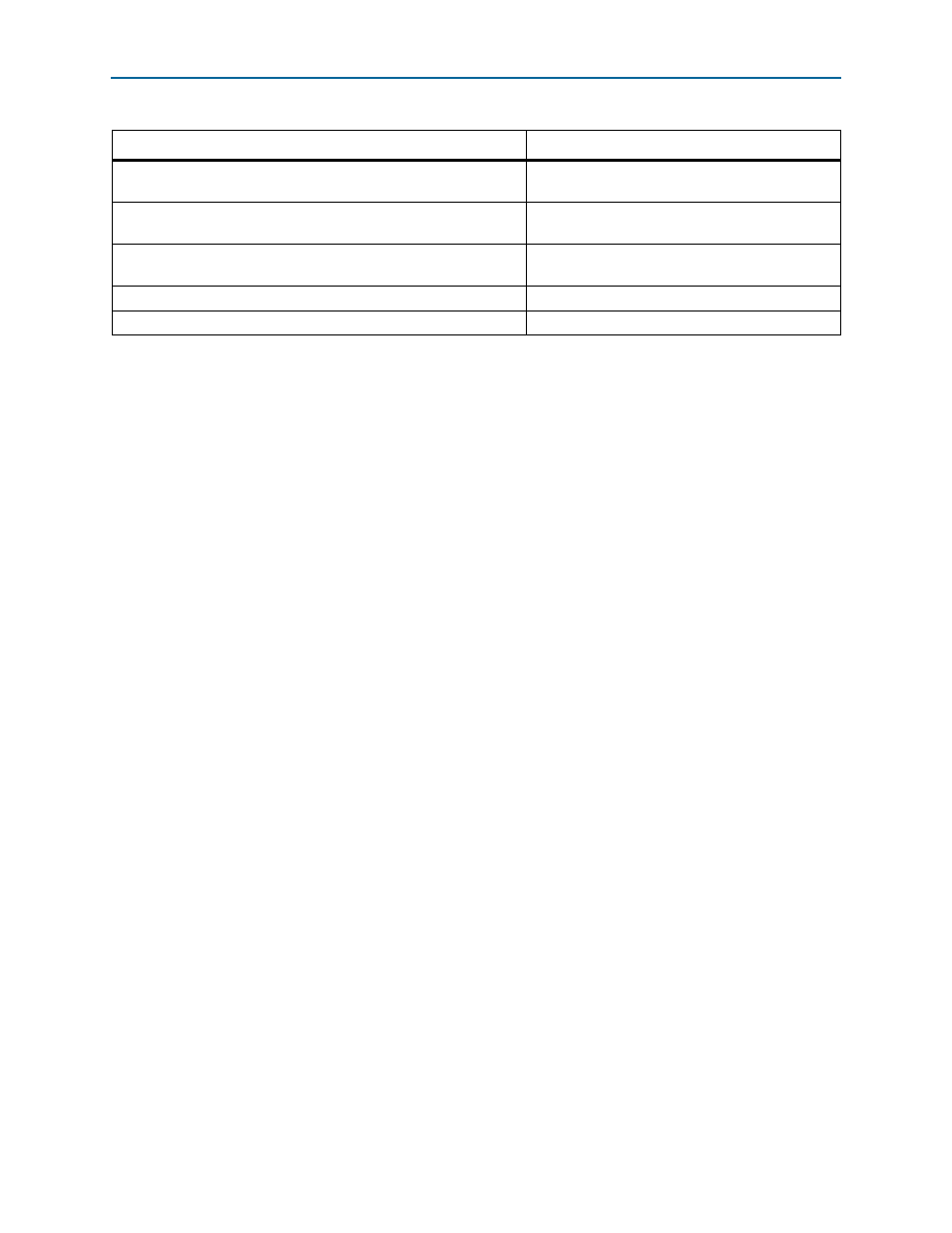

Verifies that the sister _rio module has the interrupt bit

PACKET_STORED

set

Read register at address 0x10080

Retrieves the Port-Write payload from the sister_rio module and

checks for data integrity

Read registers at addresses 0x10260–0x1029C

Checks the sister_rio module Rx Port Write Status register for

correct payload size

Read register at address 0x10254

Clears the PACKET_STORED interrupt in the sister_rio module

Write 1 to bit 4 of register at address 0x10080

Waits for the next interrupt at the sister _rio module

Monitor sister_sys_mnt_s_irq

Table 7–5. Port-Write Test

Operation

Action