Adding and connecting other system components, Adding and connecting other system components –6 – Altera RapidIO MegaCore Function User Manual

Page 180

8–6

Chapter 8: Qsys Design Example

Running Qsys

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

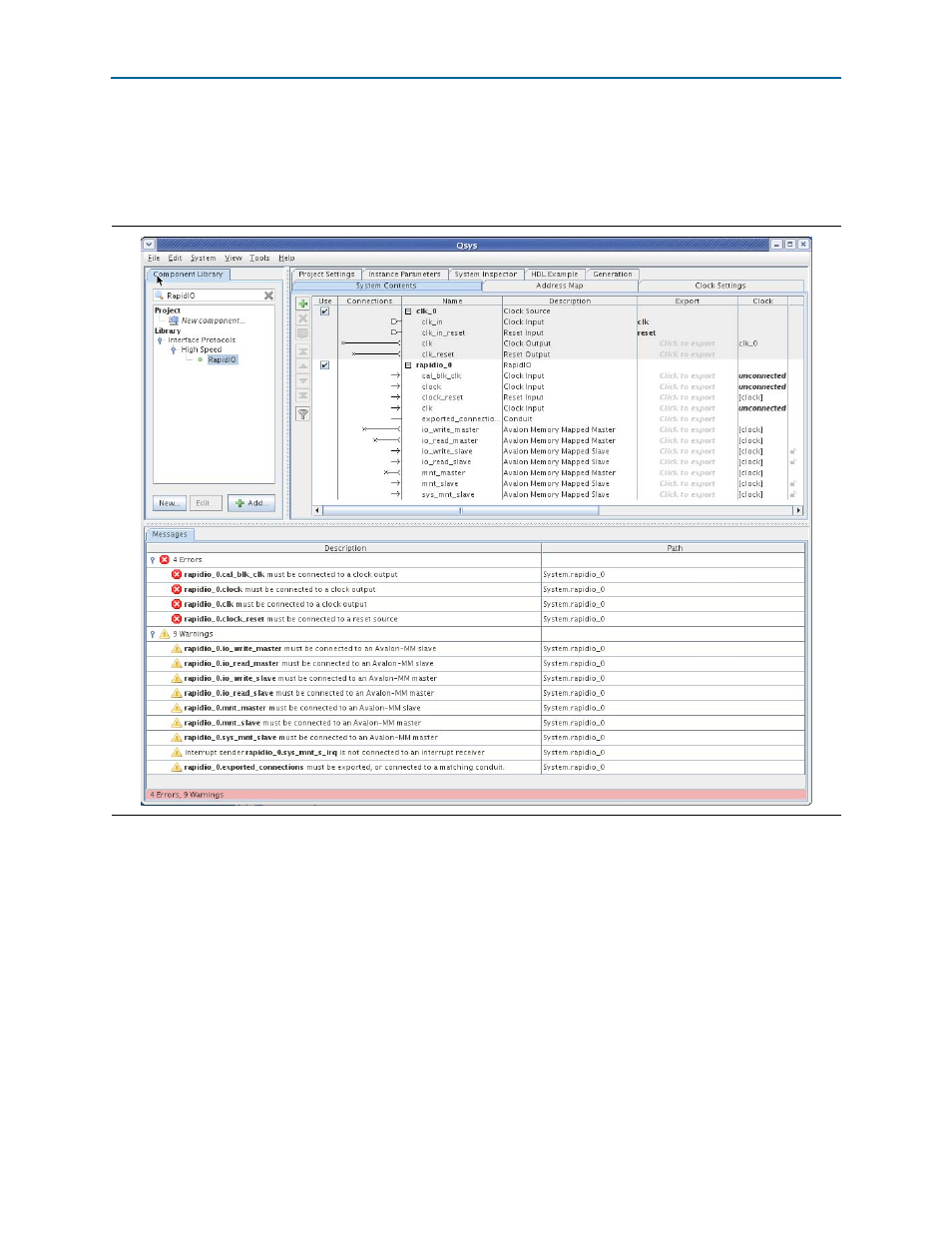

After you add the RapidIO IP core component to your system, various

Avalon-MM ports are created and shown as connection points in the System

Contents

tab. Error messages indicate that these ports are not connected, as shown

.

These errors are resolved as you add the remaining components to your system and

make all of the appropriate connections, as described in the following sections.

The default instance name of the RapidIO IP core component is rapidio_0. To run the

design example, you must retain the default name. However, in your own system,

you can change any default component instance name by right-clicking on the name

and then clicking Rename. The component name must be unique; it cannot be the

same name as the system name.

Adding and Connecting Other System Components

To complete your testbench system, you add and connect the following components,

assign addresses, and set the clock frequency:

■

Master Maintenance BFM

Figure 8–2. RapidIO IP core Added and Avalon-MM Ports Created