Table 6–11 – Altera RapidIO MegaCore Function User Manual

Page 142

6–10

Chapter 6: Software Interface

Physical Layer Registers

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

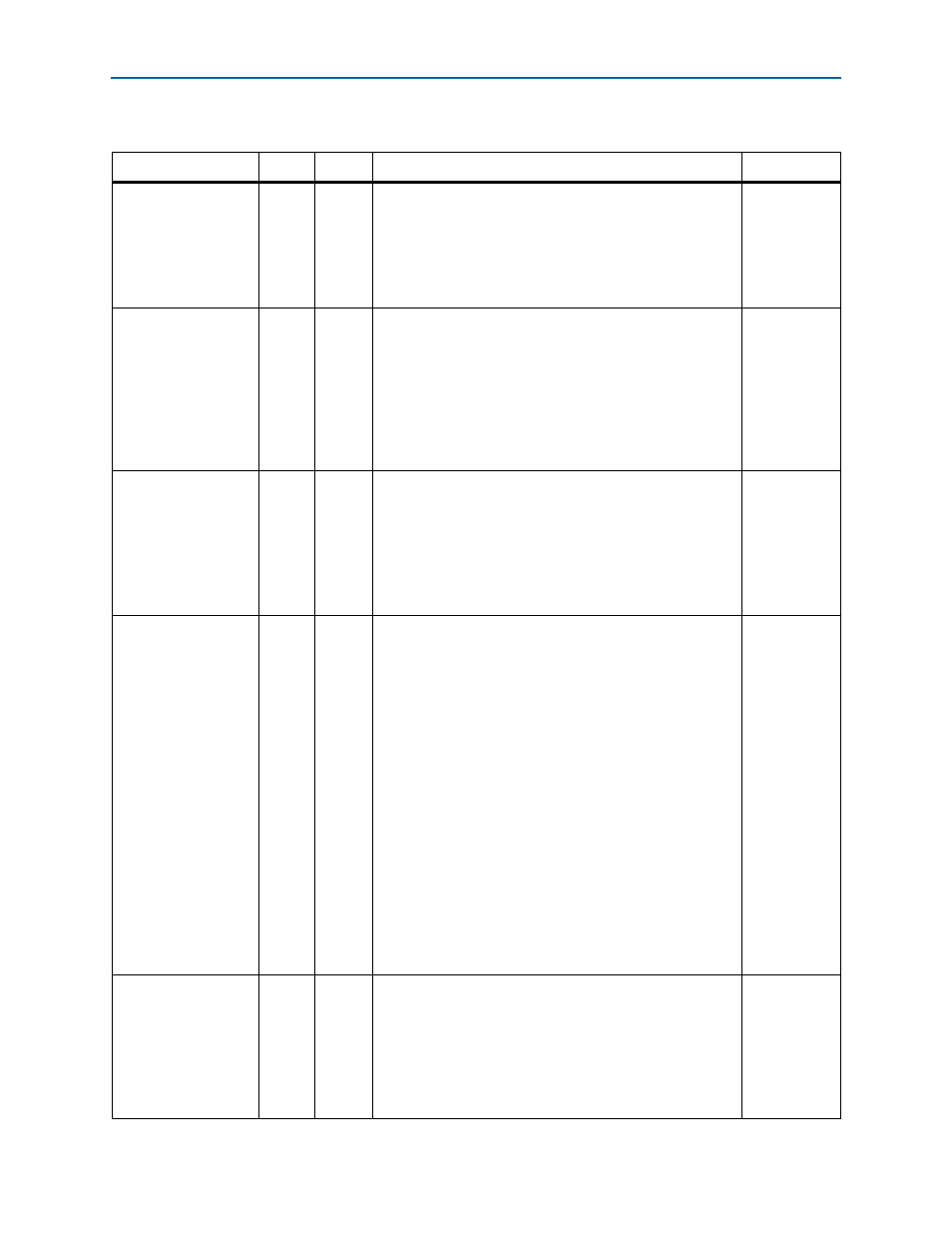

Table 6–11. Port 0 Control CSR—Offset: 0x15C (Part 1 of 2)

Field

Bits

Access

Function

Default

PORT_WIDTH

[31:30] RO

Hardware width of the port:

'b00—Single-lane port.

'b10—Two-lane port.

'b01—Four-lane port.

''b11—Reserved.

2'b00

(for 1x

variations),

2'b10

(for 2x

variations),

2'b01

(for 4x

variations)

INIT_WIDTH

[29:27] RO

Width of the ports after being initialized:

'b000—Single lane port, lane 0.

'b001—Single lane port, redundancy lane (lane 1 for 2x

variations and lane 2 for 4x variations).

'b010—Four-lane port.

'b011—Two-lane port.

‘b100 – 'b111—Reserved.

3'b000

(for

1x variations),

3'b011

(for

2x variations),

3'b010

(for

4x variations)

PWIDTH_OVRIDE

[26:24] UR0

Soft port configuration to override the hardware size:

'b000—No override.

'b001—Reserved.

'b010—Force single lane, lane 0.

'b011—Force single lane, redundancy lane.

'b100–'b111—Reserved.

3'b000

PORT_DIS

[23]

RW

Port disable:

'b0—Port receivers/drivers are enabled.

'b1—Port receivers are disabled, causing the drivers to

send out idles.

■

When this bit transitions from 1 to 0, the initialization state

machines’ force_reinit signal is asserted. This

assertion causes the port to enter the SILENT state and to

attempt to reinitialize the link, as described in section 4.12

of Part 6: LP-Serial Physical Layer Specification of the

RapidIO Interconnect Specification, Revision 2.1.

■

When reception is disabled, the input buffers are kept

empty until this bit is cleared.

■

When PORT_DIS is asserted and the drivers are disabled,

the transmit buffer are reset and kept empty until this bit is

cleared, any previously stored packets are lost, and any

attempt to write a packet to the atx Atlantic interface is

ignored by the Physical layer. New packets are NOT stored

for later transmission.

1'b0

OUT_PENA

[22]

RW

Output port transmit enable:

'b0—Port is stopped and not enabled to issue any packets

except to route or respond to I/O logical MAINTENANCE

packets, depending upon the functionality of the

processing element. Control symbols are not affected and

are sent normally.

'b1—Port is enabled to issue packets.

1'b1