Receive maintenance registers, Receive maintenance registers –17, Table 6–28 – Altera RapidIO MegaCore Function User Manual

Page 149: Table 6–27 on, Table 6–27, Describe the

Chapter 6: Software Interface

6–17

Transport and Logical Layer Registers

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

Receive Maintenance Registers

describes the receiver maintenance register.

PACKET_DROPPED

[5]

RW1C

A received port-write packet was dropped. A port-write packet is

dropped under the following conditions:

■

A port-write request packet is received but port-write

reception has not been enabled by setting bit

PORT_WRITE_ENABLE

in the Rx Port Write Control

register.

■

A previously received port-write has not been read out from

the Rx Port Write register.

1'b0

PACKET_STORED

[4]

RW1C

Indicates that the IP core has received a port-write packet and

that the payload can be retrieved using the System

Maintenance Avalon-MM slave interface.

1'b0

RSRV

[3]

RO

Reserved

1'b0

RSRV

[2]

RO

Reserved

1'b0

WRITE_OUT_OF_BOUNDS

[1]

RW1C

If the address of an Avalon-MM write transfer presented at the

Maintenance Avalon-MM slave interface does not fall within any

of the enabled Tx Maintenance Address translation windows,

then it is considered out of bounds and this bit is set.

1'b0

READ_OUT_OF_BOUNDS

[0]

RW1C

If the address of an Avalon-MM read transfer presented at the

Maintenance Avalon-MM slave interface does not fall within any

of the enabled Tx Maintenance Address translation windows,

then it is considered out of bounds and this bit is set.

1'b0

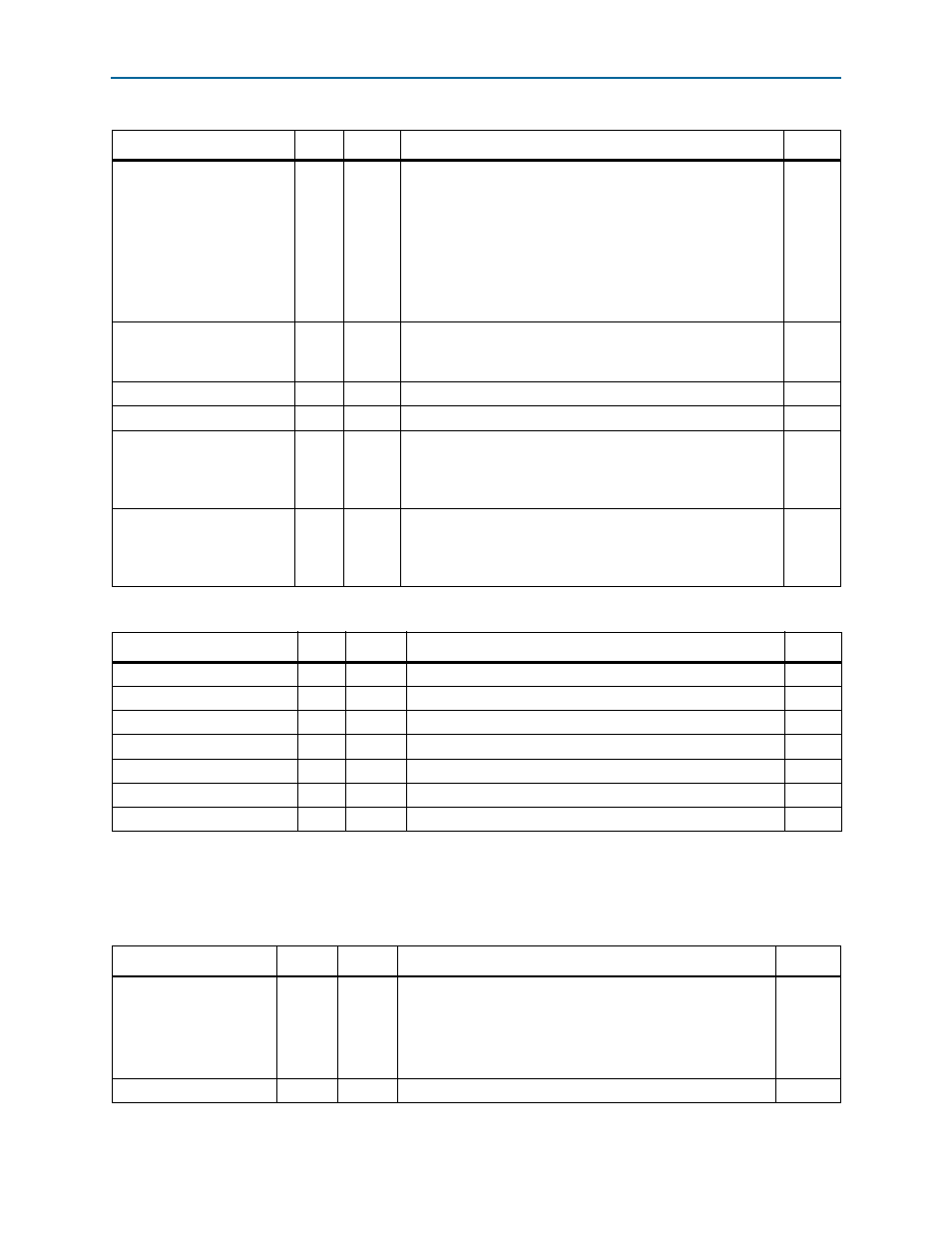

Table 6–26. Maintenance Interrupt—Offset: 0x10080 (Part 2 of 2)

Field

Bits

Access

Function

Default

Table 6–27. Maintenance Interrupt Enable—Offset: 0x10084

Field

Bit

Access

Function

Default

RSRV

[31:7] RO

Reserved

25'h0

PORT_WRITE_ERROR

[6]

RW

Port-write error interrupt enable

1'b0

RX_PACKET_DROPPED

[5]

RW

Rx port-write packet dropped interrupt enable

1'b0

RX_PACKET_STORED

[4]

RW

Rx port-write packet stored in buffer interrupt enable

1'b0

RSRV

[3:2]

RO

Reserved

2'b00

WRITE_OUT_OF_BOUNDS

[1]

RW

Tx write request address out of bounds interrupt enable

1'b0

READ_OUT_OF_BOUNDS

[0]

RW

Tx read request address out of bounds interrupt enable

1'b0

Table 6–28. Rx Maintenance Mapping—Offset: 0x10088

Field

Bits

Access

Function

Default

RX_BASE

[31:24]

RW

Rx base address. The offset value carried in a received

MAINTENANCE

Type packet is concatenated with this RX_BASE

to form a 32-bit Avalon Address as follows:

Avalon_address

= {rx_base, cfg_offset, word_addr,

2'b00}

8'h0

RSRV

[23:0]

RO

Reserved

24'h0