Qsys design example, Chapter 8. qsys design example, Chapter 8, qsys design example – Altera RapidIO MegaCore Function User Manual

Page 175: Qsys system

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

8. Qsys Design Example

The design example in this chapter shows you how to use Qsys to build a system that

combines a RapidIO IP core with other Qsys components. Qsys automatically

generates simulation models and HDL files that include all the specified components

and interconnections. The design example includes a testbench to simulate the Qsys

system you generate. However, this design example does not support programming

your target Altera device and verifying your design in hardware.

The Qsys design example is available only for non-Arria 10 IP core variations.

f

For more information about the system interconnect fabric, refer to th

chapter in volume 1 of the Quartus II

Handbook. For more information about the Qsys integration tool, refer to the

System

Design with Qsys sect

Quartus II Handbook.

The design example explains how to use Qsys, an integral feature of the Quartus II

software, to generate a system containing the following components:

■

RapidIO IP core

■

On-Chip Memory

■

Two Master BFMs

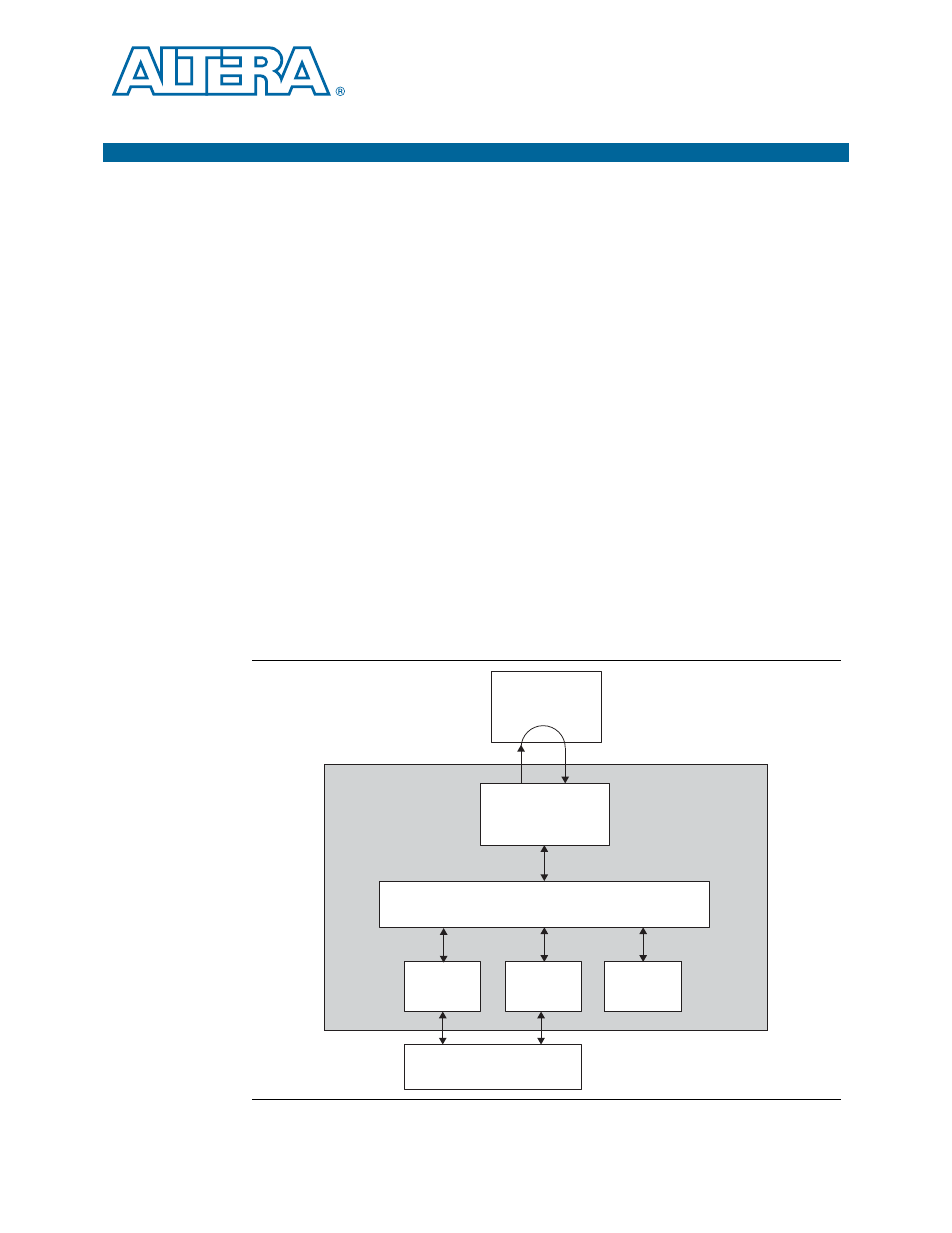

shows a block diagram of the system you create in this chapter.

Figure 8–1. Simulation Example Qsys System

RapidIO

Loopback Module

(test_bench.v)

System Interconnect Fabric

On-Chip

Memory

Qsys System

RapidIO

MegaCore Function

Avalon-MM

Master BFM

Avalon-MM

Master BFM

RapidIO Simulation Testbench

(rio_sys_tb.v)